No post anterior expliquei um pouco sobre o meio somador de 1-bit (half adder). Esse circuito é importante para que possamos criar o circuito que será apresentado a seguir, o somador completo de 1-bit (1-bit full adder, em inglês). O circuito somador completo pode ser representado por três entradas, A, B e Carry de entrada, ou Carry In, que são somados e obtemos o resultado da soma, ou sinal S de saída, e Carry de Saída, ou Carry Out. A tabela verdade pode ser representada conforme a tabela a seguir para diferentes valores de entrada.

Obtemos assim a função que melhor representa as saídas digitais desse circuito. As equações estão representadas abaixo. A soma é o resultado da operação de Ou Exclusivo, ou XOR entre A, B e Carry In. Carry Out é o resultado da operação OR de três diferentes resultados: da operação de (A.B), da operação (A.Cin) e (B.Cin). Para revisar a operação das portas lógicas, acesse o link.

Representação do Circuito Somador Completo em Diagrama de Bloco

Partindo-se então do circuito meio somador de 1-bit, percebemos que podemos conectar dois circuitos meio somador e utilizar uma porta OR para podermos obter o valor da saída Cout. Assim obtemos o circuito Somador Completo de 1-bit. Veja a figura a seguir:

Representação do Circuito Somador Completo com portas lógicas simples:

Substituindo o circuito acima por portas lógicas, conforme o que foi visto no post sobre Meio Somador, obtemos o seguinte circuito com 5 portas lógicas, que representa o Somador completo de 1-bit.

Representação do Circuito Somador Completo em Verilog:

Implementei utilizando dois módulos. O módulo meio somador foi declarado e escrito conforme explicado no post anterior. O módulo somador foi implementado de forma estrutural, então utilizou dois meio somadores e uma porta OR conforme o diagrama de blocos acima.

Arquivo meio_somador.v

module meio_somador (A, B, S, C); input A, B; output S, C; assign S = A ^ B; assign C = A & B; endmodule

Arquivo SOMADOR.v

// Embarcados - Use como quiser e de os creditos // Exemplo de Implementacao de um somador completo de 1bit // Thiago Lima - 14/11/2015 module SOMADOR (A, B, Cin, Soma, Cout); input A, B, Cin; output Soma, Cout; wire Carry_1, Carry_2, Soma_1; meio_somador U1 (A, B, Soma_1, Carry_1); meio_somador U2 (Cin, Soma_1, Soma, Carry_2); or U3 (Cout, Carry_1, Carry_2); endmodule

Testbench para o Circuito Somador Completo:

Para simular o circuito, injetei 8 sequências diferentes de sinais, para cobrir todos os casos da tabela verdade mostrada no começo do post.

module SOMADOR_tb; reg A_tb, B_tb, Cin_tb; wire Soma_tb, Cout_tb; SOMADOR dut( A_tb, B_tb, Cin_tb, Soma_tb, Cout_tb); initial begin A_tb = 1'b0; B_tb = 1'b0; Cin_tb = 1'b0; #1 A_tb = 1'b0; B_tb = 1'b1; Cin_tb = 1'b0; #1 A_tb = 1'b1; B_tb = 1'b0; Cin_tb = 1'b0; #1 A_tb = 1'b1; B_tb = 1'b1; Cin_tb = 1'b0; #1 A_tb = 1'b0; B_tb = 1'b0; Cin_tb = 1'b1; #1 A_tb = 1'b0; B_tb = 1'b1; Cin_tb = 1'b1; #1 A_tb = 1'b1; B_tb = 1'b0; Cin_tb = 1'b1; #1 A_tb = 1'b1; B_tb = 1'b1; Cin_tb = 1'b1; #1; end endmodule

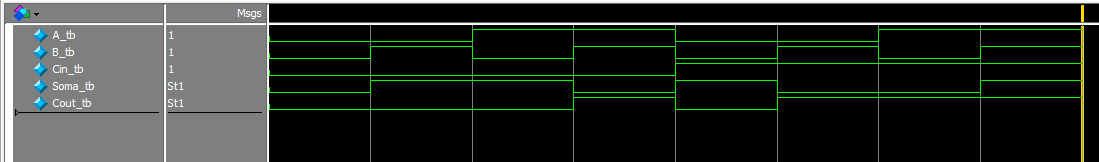

Forma de onda resultante do teste:

A forma de onda resultante foi de acordo com o esperado.

Caso queira reproduzir o teste feito acima, faça Download do Projeto para o Quartus da Altera e aperte o play:

Circuito Somador Completo (Full Adder) com NANDs:

Vamos então apresentar o circuito Somador Completo projetado em Portas NAND. Este circuito é mais rápido, em termos de propagação da onda pelo circuito. Isso é explicado se compararmos com os outros circuitos para o mesmo circuito Somador Completo e sua construção em termos de transistors (CMOS). Substituindo as portas lógicas XOR por portas NANDs (para ver mais detalhes sobre como obter esse circuito, acesse o post onde explico sobre isso), é possível, a partir do circuito acima, substituir os componentes por portas NANDs e obter o seguinte circuito resultante:

Representação do Circuito Somador (Full Adder) com NANDs em Verilog:

Esse código não tem segredo, apenas representei as portas lógicas NANDs conforme o circuito acima em Verilog. Utilizei o mesmo testbench. O resultado também foi o mesmo.

// Embarcados - Use como quiser e de os creditos // Exemplo de Implementacao de um somador completo de 1bit // Thiago Lima - 14/11/2015 module SOMADOR (A, B, Cin, Soma, Cout); input A, B, Cin; output Soma, Cout; wire C, D, E, F, G, H, I; nand U1 (C, A, B); nand U2 (D, C, A); nand U3 (E, C, B); nand U4 (F, D, E); nand U5 (G, F, Cin); nand U6 (H, G, Cin); nand U7 (I, F, G); nand U8 (Soma, I, H); nand U9 (Cout, G, C); endmodule

Caso queira reproduzir o teste feito acima, faça Download do Projeto para o Quartus da Altera e aperte o play:

O Esquemático que obtemos é o seguinte:

Este Esquemático será utilizado para fazer somadores maiores, conforme veremos nos próximos artigos.

Deixem seus comentários e críticas abaixo.