O projeto demonstrado aqui é baseado no circuito original apresentado por Malvino. O SAP-1 é construído com circuitos integrados, já neste projeto foram utilizados os blocos do simulador logsim que não tem relação com modelo e/ou fabricantes desses componentes. A visão do do projeto do SAP-1 construído no simulador é mostrada na Figura 1.

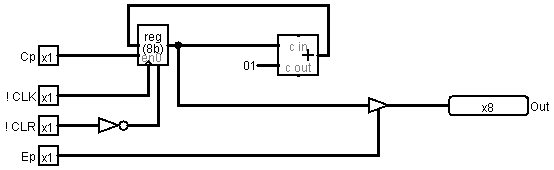

Contador de Programa

O contador de programa, mostrado na Figura 2, é representado por um registrador de 4 bits conectado a um circuito somador. Assim, uma das entradas do circuito somador é o valor atual de PC e a outra o valor 1. Esse circuito é controlado pelo sinal Cp, ativado no estado T2, que é responsável por habilitar o registrador durante o pulso de clock (!CLK). Além desses sinais, o registrador pode ser reiniciado a partir da entrada CLR. Já sua conexão com o barramento W é feita por um buffer tri-state controlado pelo sinal Ep.

Cabe ressaltar que o mesmo procedimento pode ser implementado por um conjunto de flip-flops, formando um contador assíncrono. Esse é o caso do projeto real do SAP-1.

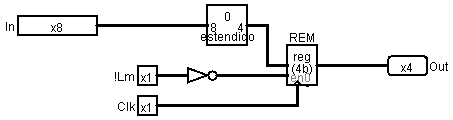

Registrador de Endereços de Memória

O registrador REM, mostrado da Figura 3, é controlador pelo sinal !Lm. Durante o pulso de clock esse registrador armazenará os 4 bits menos significativos do barramento W. Esse valor é utilizado para endereçar a memória RAM.

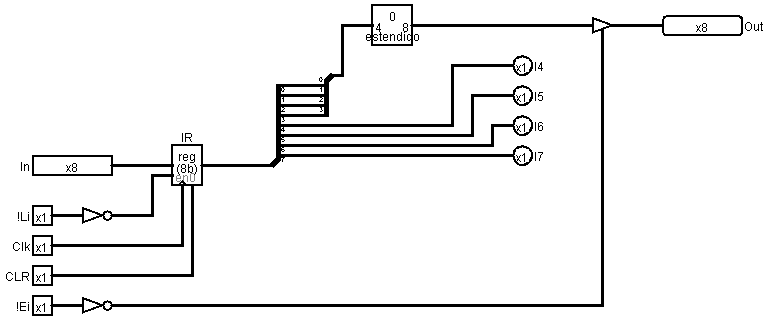

Registrador de Instruções

O registrador de instruções, mostrado na Figura 4, é composto por um elemento de memória de 8 bits. Esse registrador é controlado pelo sinal !Li que é responsável por habilitar o registrador durante o pulso de clock. Além desses sinais, o registrador pode ser reiniciado a partir da entrada CLR. Já sua conexão com o barramento W (somente os 4 bits menos significativos) é feita por um buffer tri-state controlado pelo sinal Ei. Cabe ressaltar que os 4 bits mais significativos determinam o código de operação da instrução, que é utilizado pela unidade de controle.

Registrador Acumulador

O registrador acumulador, mostrado na Figura 5, é composto por um elemento de memória de 8 bits. Esse registrador é controlado pelo sinal !La que é responsável por habilitar o registrador durante o pulso de clock CLK. Além desses sinais, o registrador é conectado ao módulo somador/subtrator, já sua conexão com o barramento W é feita por um buffer tri-state controlado pelo sinal Ea.

Registrador B

O registrador B, mostrado na Figura 6, é composto por um elemento de memória de 8 bits. Esse registrador é controlado pelo sinal !Lb que é responsável por habilitar o registrador durante o pulso de clock CLK. Esse registrador tem conexão apenas com o módulo somador/subtrador.

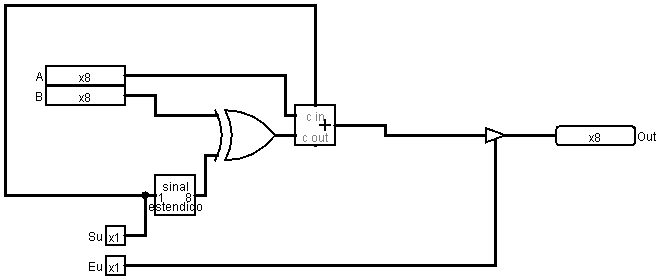

Módulo Somador/Subtrator

O módulo somador/subtrator é mostrado na Figura 7. Basicamente, esse circuito é composto de um elemento somador. Para realizar o processo de subtração a representação de valores em complemento de 2 é utilizada. Além disso, sua conexão com o barramento W é feita por um buffer tri-state controlado pelo sinal Eu.

Para entender sua operação, considere que o sinal Su em zero indica a operação de adição. Fazendo a operação XOR de B com 8 bits (com valores iguais ao de Su), temos o mesmo valor de B, isto é, qualquer valor XOR com zero resulta no mesmo valor. Dito de outra maneira, na operação de adição o circuito XOR não tem função. Além disso, com Su igual a zero, a entrada de carry in do circuito somador também não terá função. Desse modo, o resultador da operação é simplesmente A + B.

Já na operação de subtração o sinal Su será 1. Fazendo a operação XOR de B com 8 bits (com valores iguais ao de Su), temos o valor inverso de B (complemento de um), isto é, qualquer valor XOR com 1 resulta no seu complemento. Além disso, com Su igual a um, a entrada de carry in do circuito somador estará adicionado um na operação. Desse modo, o resultador da operação é simplesmente A + (~B + 1), isto é, a operação A – B. De modo resumido, o sinal Su em 1 determina o complemento de 2 da entrada B, fazendo com que a operação seja de subtração;

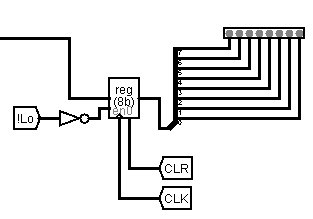

Registrador de Saída

O registrador de saída, mostrado na Figura 8, é composto por um elemento de memória de 8 bits. Esse registrador é controlado pelo sinal !Lo que é responsável por habilitar o registrador durante o pulso de clock. Esse registrador aciona um conjunto de 8 leds.

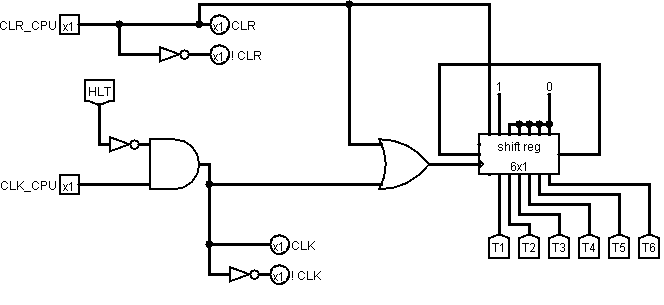

Controlador e Sequencializador

O circuito mostrado na Figura 9 apresenta o módulo contador em anel. Esse circuito é responsável por gerar os sinais de estado da unidade de controle. A cada pulso de clock o bit de valor 1 é deslocado no registrador. Esse bit tem seu valor determinado na condição de Reset. Além disso, devido à instrução HLT, o processamento é encerrado quando a instrução é decodificada. Essa operação foi implementada com uma lógica AND do sinal HLT com o pulso de clock.

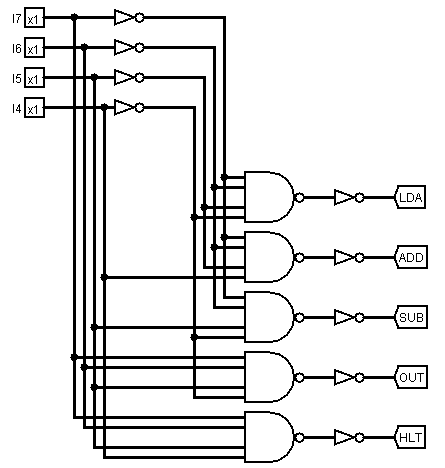

Além dos sinais de controle, esse módulo tem como entrada a instrução atual armazenada no registrador de instruções. Para cada código de entrada um valor decodificado acionará somente um dos sinais, indicando qual instrução está sendo executada. Esse circuito é mostrado na Figura 10.

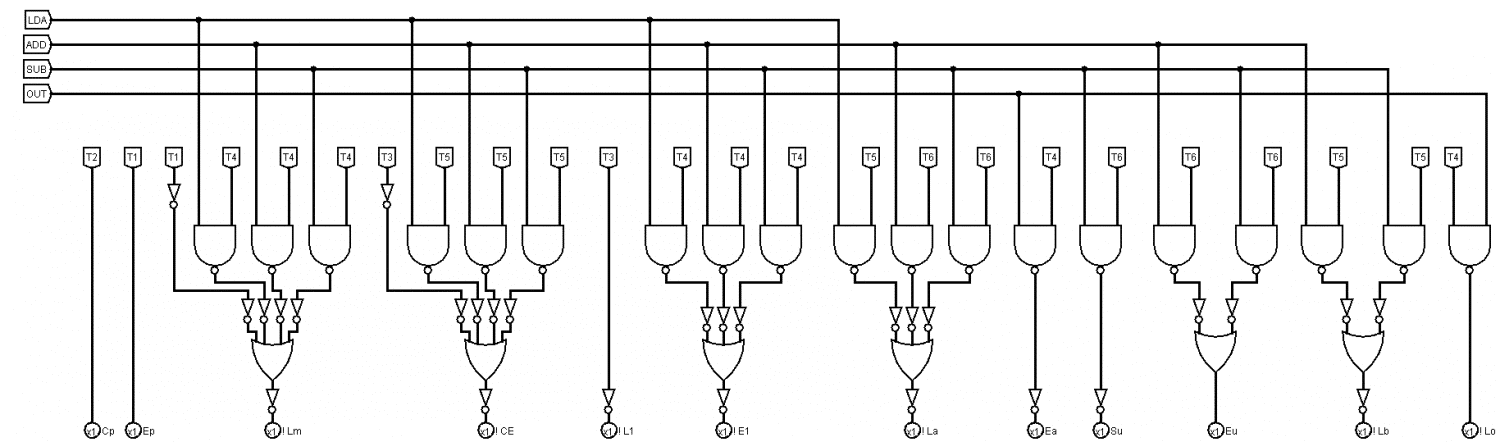

Esses sinais são utilizados como entradas da matriz de controle. A matriz de controle, mostrado na Figura 11, é o circuito lógico responsável por determinar as saídas que acionarão os outros elementos do SAP-1. Portanto, o circuito tem como entradas ativadas a instrução e o estado atual.

As funções booleanas para cada saída são mostradas abaixo:

- Cp=T2

- Ep=T1

- Li= NOT(T3)

- Ea=OUT.T4

- Su=SUB.T6

- Lo= NOT(OUT.T4)

- Lb= NOT((ADD.T5)+(SUB.T5))

- Eu=(ADD.T6)+(SUB.T6)

- La= NOT((LDA.T5)+(ADD.T6)+(SUB.T6))

- Ei= NOT((ADD.T4)+(LDA.T4)+(SUB.T4))

- CE= NOT(T3+(LDA.T5)+(ADD.T5)+(SUB.T5))

- Lm= NOT(T1+(LDA.T4)+(ADD.T4)+(SUB.T4))

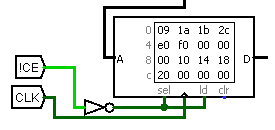

Memória RAM

A memória RAM, mostrada na Figura 12, tem como sinal de controle a entrada CE. Com esse sinal em zero, os dados do endereço selecionado são passados para o barramento W.

Executando um Programa

Para testar o SAP-1, utilizou-se o programa de exemplo do primeiro artigo. Na Figura 13 é mostrado o conteúdo da memória, em que instruções e dados são armazenados.

| Endereço | Programa | Conteúdo da Memória | Categoria |

| 0H | LDA 9H | 0000 1001 | Instruções |

| 1H | ADD AH | 0001 1010 | |

| 2H | ADD BH | 0001 1011 | |

| 3H | SUB CH | 0010 1100 | |

| 4H | OUT | 1110 0000 | |

| 5H | HLT | 1111 0000 | |

| 6H | XX | XXXX XXXX | Dados |

| 7H | XX | XXXX XXXX | |

| 8H | XX | XXXX XXXX | |

| 9H | 10H | 0001 0000 | |

| AH | 14H | 0001 0100 | |

| BH | 18H | 0001 1000 | |

| CH | 20H | 0010 0000 |

Deste modo, basta gerar os pulsos de clock para o SAP-1 entrar em operação! Para manter o clock contínuo basta pressionar CTRL+K.

Projeto

Para realizar o download do circuito e do programa de exemplo acesse os links indicados abaixo:

- [wpdm_asset id=’4′]

- [wpdm_asset id=’5′]

Referências

- [1] MALVINO, A.P. Microcomputadores e Microprocessadores. McGRAW-HILL do Brasil, 1985.

- Crédito da imagem destacada.

poderia disponibilizar para baixar

por que da erro ao baixar o arquivo do sap1 ?

Boa noite, Garcia. Tudo em paz?

Muito bom o conteúdo do artigo, parabéns.

Gostaria de ter acesso aos arquivos do logisim do projeto, teria comodisponibilizar?

Grato.

Por que não consigo fazer download do projeto ?

Que delícia de conteúdo.

Quero mais.