Introdução

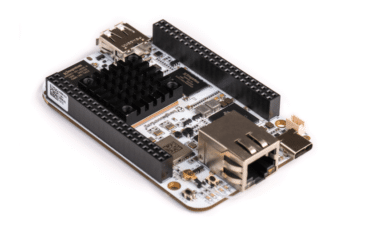

Nos nossos dois primeiros artigos, iniciamos com nossa análise detalhada do sistema de alimentação da plataforma BeagleBone Black. No primeiro artigo entendemos para que serve um PMIC, seu funcionamento e principais características. No segundo artigo, demos continuidade no estudo desse componente, dando maior ênfase em como ele é utilizado dentro da plataforma.

Neste artigo, vamos continuar estudando com detalhes as tensões geradas por esse PMIC, e onde elas são usadas na plataforma da BeagleBone Black.

Alimentação do Núcleo (VDD_CORE)

Essa alimentação é gerada pelo regulador DCDC3 e possui uma tensão fixa de 1V1 em qualquer versão do PMIC (TPS65217x), podendo chegar a 1,2A. O indutor utilizado (LQM2HPN2R2MG0L) é o mesmo que veremos nos outros dois reguladores buck. Trata-se de um indutor multilayer da Murata feito especificamente para Power Line, com o valor de 2,2uH 20%.

É interessante analisar a estratégia de layout adotada pela equipe que desenvolveu esse hardware. Embora o PMIC e o capacitor C11 estejam no Top Layer, o indutor L3 fica no Bottom Layer. Em um primeiro momento, podemos pensar que esse tipo de solução não estaria seguindo exatamente as boas práticas de layout, principalmente porque o chaveamento está sendo feito a 2,25MHz e furos de passagem são mal vistos para frequências como essa. No entanto, o objetivo principal é deixar esse capacitor de filtro bem próximo ao PMIC, pois é dele que virá o sinal de feedback do regulador. Com esse capacitor próximo, ruídos no feedback serão minimizados.

A tensão gerada é levada ao processador, passando por uma série de capacitores de desacoplamento. Esse núcleo possui um número grande de conexões para a alimentação do core. É sempre interessante adicionar capacitores de desacoplamento o mais próximo possível desses pontos de alimentação.

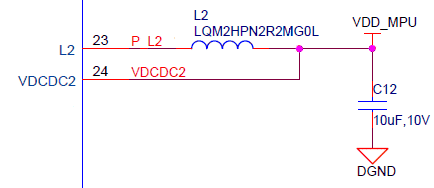

Alimentação da MPU (VDD_MPU)

Exatamente como o VDD_CORE, a tensão VDD_MPU é gerada por um regulador buck, neste caso o DCDC2. A tensão que ele fornece também é de 1V1, podendo chegar a 1,2A. O indutor e capacitor utilizados são exatamente os mesmos do DCDC3 que vimos acima.

Esta alimentação é fornecida apenas para o núcleo do sistema, passando apenas por alguns capacitores de desacoplamento. O interessante dessa alimentação é que a CPU fornece um ponto de checagem, presente como um test-point (TP2) que pode ser verificado abaixo.

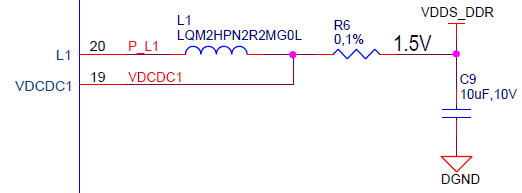

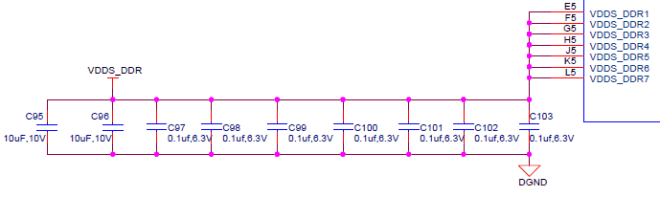

Alimentação das memórias RAM (VDDS_DDR)

A tensão VDDS_DDR alimenta tanto a memória da plataforma, como também o periférico do núcleo responsável pela comunicação com ela. Fornecida pelo DCDC1 na tensão de 1V5, podendo esta também chegar a 1,2A. Essa tensão é conectada através de R6, que apenas faz a conexão entre a fonte e a via de alimentação.

Assim como visto em outro regulador, a estratégia de layout colocou o indutor L1 no Bottom Layer, com o resistor R6 bem próximo a ele, e o capacitor C9 no Top Layer. Da mesma forma, o capacitor fixa muito próximo ao próprio PMIC, onde é feita a análise do sinal de feedback.

Essa tensão é levada para o núcleo, tendo apenas uma série de capacitores de desacoplamento ligada a ele.

Uma vez que essa alimentação chega na memória, temos um circuito mais interessante. Assim como a maioria dos dispositivos, essa alimentação possui uma série de capacitores de desacoplamento e alimenta a memória RAM. O VDDS_DDR também é utilizado com um resistor de pull-up (R97 de 1K5) para o sinal de DDR_RESETn. Esse sinal é controlado por um pino específico vindo do núcleo.

Também vamos encontrar uma tensão em um divisor resistivo criando o sinal DDR_VREF, aplicando diretamente em VREF_CA e VREF_DQ. Trata-se da metade da alimentação, neste caso 0,75V. Analisando o MT41K256M16HA, da Micron, verificamos que VREF_CA significa “Reference Voltage for Control, Command and Address” (Tensão de referência para controle, comando e endereço – em uma tradução livre). O documento do componente também indica que essa tensão precisa ficar em 50% da alimentação, podendo apenas variar entre 49% e 51%.

O sinal de DDR_VREF também é aplicado ao núcleo, sendo ligado diretamente ao VREFSSTL. Abaixo podemos verificar não apenas essa ligação, como também o sinal de DDR_RESETn gerado pelo AM335x.

Alimentação de 1V8 (VDD_1V8)

A alimentação de 1V8 vem diretamente do LDO3, que suporta até 400mA. Já vimos este regulador no artigo passado, podendo alimentar VDDS, mas desligado pelo resistor R9 não montado.

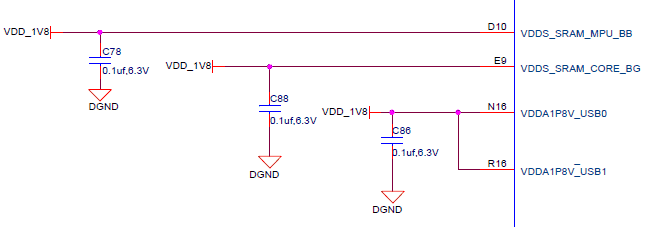

O importante desse regulador é que, além de alimentar um bloco importante do núcleo, será a base do VDD_PLL, VDD_ADC e HDMI_1V8. Para o núcleo, a alimentação é dada conforme abaixo.

Alimentação do conversor AD (VDD_ADC e GNDA_ADC)

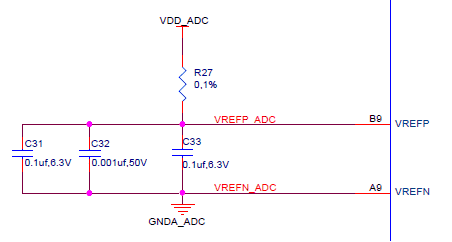

Essa alimentação é derivada do VDD_1V8, passando por um filtro passa-baixa formado pelo indutor FB2 e FB3, e os capacitores C93, C31, C32 e C33. Isso garante que qualquer ruído gerado na linha de alimentação, será minimizado para a alimentação do conversor ADC. A boa prática de separar os sinais de terra também foi respeitada, existindo o terra analógico e o terra digital.

Os sinais de referência desse conversor também respeitam a alimentação, sendo o VDD_ADC a referência VREF+, e GNDA_ADC a referência de VREF-. Não há como alterar o sinal de referência diretamente, mesmo existindo o resistor R27.

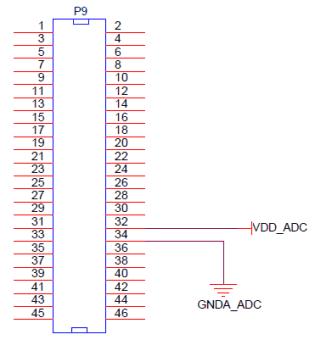

A alimentação VDD_ADC e GNDA_ADC são externados pelo conector P9.32 e P9.34, respectivamente. Esse nível de tensão pode ser utilizado como a referência de VREF para um circuito externo. Apesar de ser possível alterar a plataforma para utilizar uma alimentação VDD_ADC externa, não há grande vantagem. Isso porque a tensão precisa ser fixa em 1V8 com um erro máximo de 5%.

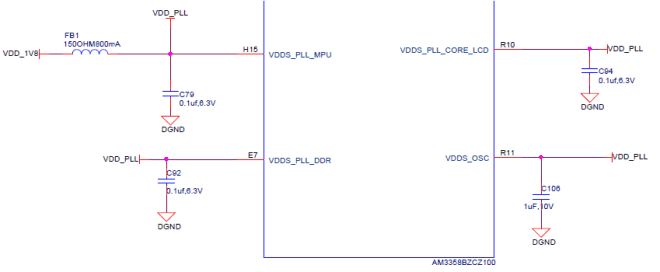

Alimentação da PLL (VDD_PLL)

Assim como VDD_ADC, o VDD_PLL também é derivado do VDD_1V8. Da mesma forma, o sinal é filtrado por um filtro passa baixa formado pelo indutor FB1 e os capacitores C79, C92, C94 e C106. Como se trata apenas da alimentação da PLL, não há muitas novidades nesse circuito além do filtro.

Alimentação da HDMI (HDMI_1V8)

Uma das grandes vantagens da BeagleBone Black em relação a outras plataformas é a saída de vídeo HDMI. No entanto, o núcleo AM335x não está preparado para esse tipo de saída, gerando apenas sinais para LCD.

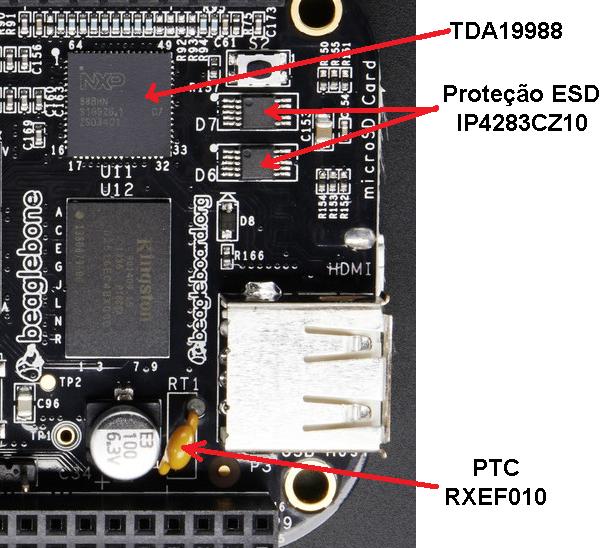

Para apresentar uma saída mais fácil de se trabalhar, a equipe do projeto fez uso de um componente da NXP para fazer essa conversão. Trata-se do TDA19988, aqui presente como U11. Esse componente faz a conversão dos sinais específicos para o LCD para o formato HDMI. Futuramente vamos falar mais sobre este componente. Por enquanto vamos nos ater apenas à alimentação.

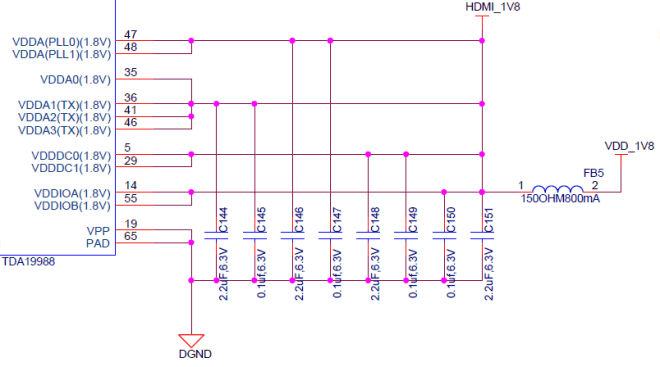

Assim como boa parte dos periféricos do núcleo, este componente exige 1V8 de alimentação. Como vimos mais acima, essa alimentação é derivada de VDD_1V8. Da mesma forma que o conversor ADC, essa tensão é fornecida através de um indutor, fazendo um filtro passa baixa utilizando uma série de capacitores.

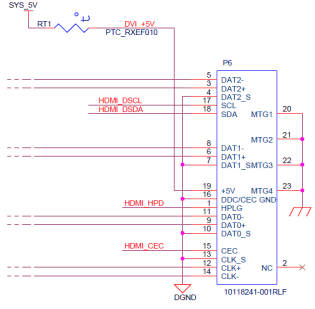

Alimentação do DVI (DVI_+5V)

É interessante que o padrão HDMI exige o fornecimento de 5V no conector. Para fazer isso, mas manter uma proteção, a equipe adicionou um PTC nessa alimentação.

O que está por vir

No próximo artigo vamos terminar de analisar os canais de alimentação e principais componentes responsáveis pelas regulagens da plataforma. Assim, poderemos dar sequência na análise do resto do hardware. O objetivo desses artigos é permitir a criação de Capes e hardwares derivados.