Introdução

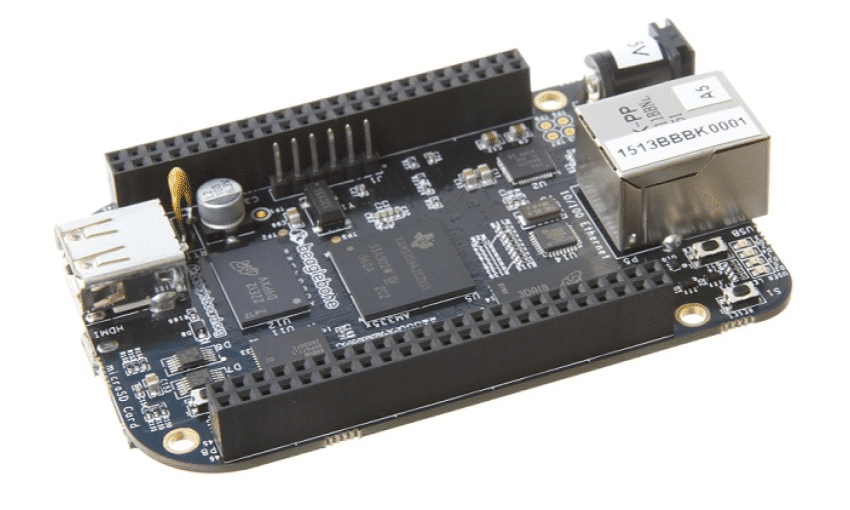

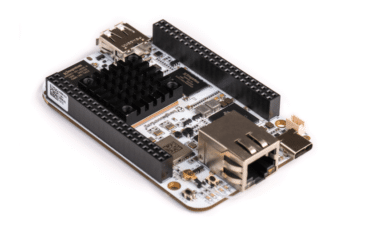

Dando sequência nos artigos sobre a alimentação da plataforma BeagleBone Black, vamos analisar os últimos níveis de tensão desse sistema. Nos artigos anteriores verificamos qual a estratégia adotada para este circuito, os principais componentes e a maioria das linhas de alimentação. Neste artigo vamos verificar as linhas restantes.

Esses artigos serão a base de uma análise aprofundada do hardware desse sistema. Servirão como fundamentos para a criação de “Capes” e a elaboração de hardwares derivados.

Alimentação de principal de 3V3 (VDD_3V3A)

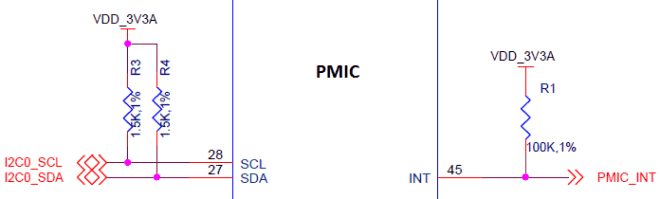

Essa alimentação é gerada pelo LDO4, sendo fixa em 3,3V para o nosso PMIC. Pode fornecer até 400mA e alimenta uma série de circuitos do sistema, começando pelo próprio PMIC, onde os resistores de pull-up da comunicação I2C possuem essa alimentação como referência. No mesmo componente, alimenta o pull-up para a interrupção.

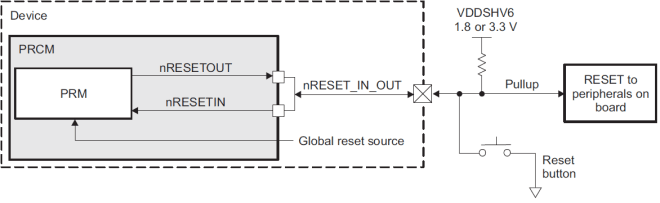

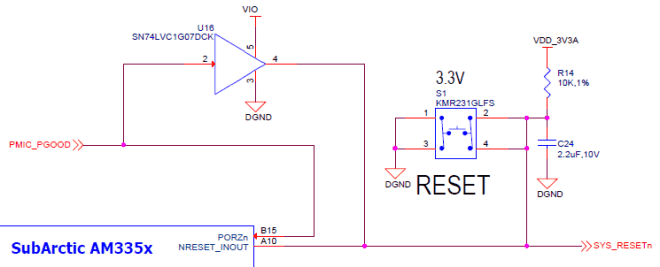

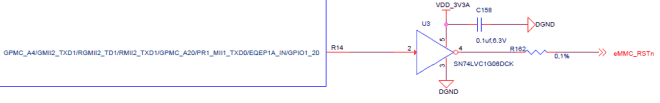

Essa tensão também é responsável pelo funcionamento do circuito de reset. Trata-se de uma montagem clássica com um circuito RC formado pelo R14 e C24, onde o capacitor começa descarregado e, no momento que a alimentação se apresenta, este começa a carregar.

É interessante verificar que a estratégia de layout colocou esses dispositivos próximos ao JTAG, em vez de deixar próximo ao botão de Reset (S1), ou mesmo ao processador.

Segundo a documentação do AM335x, esse dispositivo considera como nível baixo qualquer tensão inferior a 0,8V (para entender melhor, segue um artigo sobre os Níveis de Tensão). Como o estado de reset é mantido em nível baixo, podemos garantir que ele se manterá em reset ao menos até o capacitor chegar a essa tensão. Assim, considerando a carga do capacitor segue a seguinte fórmula:

Temos então que:

Logo, temos a certeza que o sistema permanecerá em Reset ao menos durante 6,1mS.

O circuito integrado SN74LVC1G06DCK (U3) também é alimentado pelo LDO4. Trata-se de um inversor open-drain, responsável por gerar o sinal de reset para a memória eMMC do dispositivo. A referência de nível alto para este sinal é dado por R111, fornecido por outra fonte de alimentação, conforme veremos mais adiante.

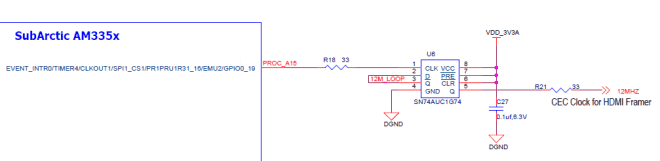

A alimentação VDD_3V3A também alimenta o SN74AUC1G74 (U6). Este componente é um flip-flop do tipo D, configurado especificamente para fazer a divisão do clock. Dessa forma, a saída terá duty-cycle de 50%. Esse sinal é especificamente para o circuito do HDMI.

Outro oscilador alimentado pela linha de VDD_3V3A é o Y4. Trata-se de um circuito gerador de clock de 24,576MHz. O BOM desse circuito indica que é possível selecionar até três possíveis opções para esse oscilador, ASDMB-24.576MHZ-LC-T da Abracom, ECS-2033-24.576-B da ECS Inc e ISM95-3161BH-24.576 da ILSI. Todas elas têm precisão de 50ppm e são compatíveis com CMOS/TTL.

Esta linha de alimentação também é responsável pelos 3V3 do núcleo e do circuito de USB. Os canais VDDA3P3V_USB0 e VDDA3P3V_USB1 são alimentados por esse regulador, assim como as entradas VDDSHVxx.

No datasheet do núcleo é possível verificar o que é alimentado por cada linha de alimentação. Podemos, então, verificar que a linha VDDSHVxx alimenta a maioria dos periféricos presentes no AM335x. É por essa alimentação que são gerados os sinais de 3V3 dos GPIOs, UARTs, SPIs, MMC, etc.

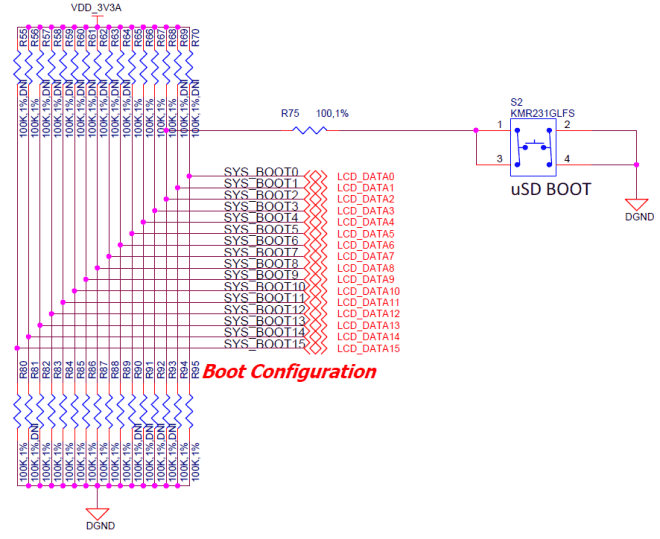

Outro bloco fundamental alimentado pelo VDD_3V3A é a configuração de BOOT do sistema. Tratam-se de resistores de pull-up e pull-down que, de acordo com sua configuração montado/não-montado determinam por qual dispositivo o sistema vai inicializar. Nesse momento, nossa análise está se preocupando apenas em conhecer os pontos alimentados por cada canal dos reguladores. Dessa forma, deixaremos para avaliar o que cada resistor define nessa configuração em um momento futuro.

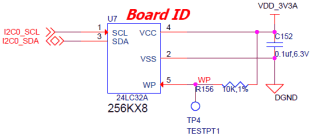

Finalizando o VDD_3V3A, mas não menos importante, vamos analisar a memória I7. Trata-se de uma Serial EEPROM 24LC32A, que comunica através do barramento I2C . Esse dispositivo possui gravado informações sobre a plataforma, que pode ser lido pelo barramento I2C, compartilhado nas barras de extensão.

Alimentação secundária de 3V3 (VDD_3V3B)

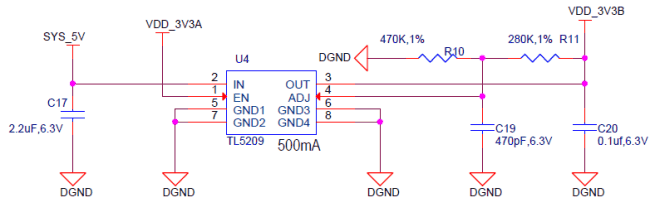

Esta alimentação é a única que não é fornecida pelo PMIC. Trata-se de um regulador LDO TL5209, da Texas Instruments, que pode fornecer até 500mA. A entrada dessa alimentação vem diretamente do SYS_5V, sendo este regulador ajustável através dos resistores R10 e R11. Como vimos anteriormente, quem habilita essa tensão é o VDD_3V3A. A documentação indica claramente que isso é feito para se reduzir o delay nas linhas de 3V3, conforme a versão A6 da plataforma.

“Moved the enable for the VDD_3V3B regulator to VDD_3V3A rail. Change was made to reduce the delay between the ramp up of the 3.3V rails.”

“Movido a habilitação para o regulador VDD_3V3B para a linha de VDD_3V3A. Esta alteração foi feita para reduzir o atraso entre a subida nas linhas de 3,3V.” – Em uma tradução livre.

É importante perceber que, mesmo reduzindo esse delay, esse regulador apenas alimenta dispositivos externos ao núcleo. Dessa forma, quando a linha VDD_3V3B estiver estabilizada, a linha principal VDD_3V3A já estará em pleno funcionamento.

Para o nosso caso, o regulador foi calculado para Vo = 1,242 ( 1 + R10/R11) = 3,327V. Considerando apenas as tolerâncias dos resistores (1%), essa tensão pode variar apenas 1,25% (de 3,369V a 3,286V), sendo assim bastante estável. Uma série de circuitos são alimentados com esse regulador nesta plataforma. Podemos observar essa linha de alimentação no conector do JTAG P2, tanto como referência de pull-up (R23 e R24), como própria alimentação (P2.5).

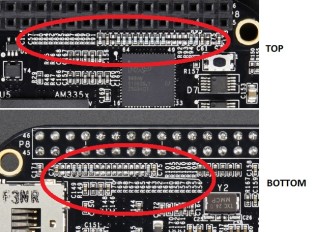

Um adendo referente ao layout desse conector é a posição do pino 1. Em um primeiro momento, não é possível verificar qual é a posição correta, uma vez que não há nenhuma marcação no silk. No entanto, o System Reference Manual possui uma explicação melhor sobre a pinagem.

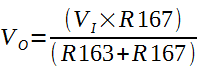

A tensão de VDD_3V3B também é passada para o núcleo na forma de uma sinal no conversor ADC. Podemos observar um divisor resistivo formado por R163 e R164 alimentando o canal 7 do ADC (AIN7). Sendo assim, o valor em AIN7 segue a seguinte regra:

Logo:

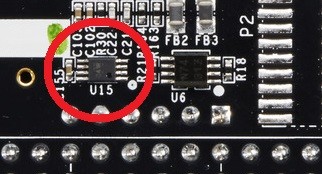

Essa tensão também alimenta o U15 (SN74LVC2G241), que faz o trabalho de buffer de sinal para a serial presente em J1. Essa é a porta serial de debug do sistema, que não está presente nos conectores P8 e P9. O buffer faz o casamento dos níveis de sinais para garantir o TTL-3V3, além de servir como proteção para o núcleo.

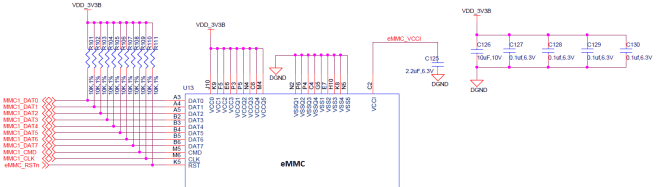

Essa alimentação também é responsável pela alimentação da eMMC da BeagleBone Black (U13). Esse componente (MTFC4GLDEA) permite uma tensão de alimentação de 2,7V a 3,6V, separadas em VCC e VCCQ. A primeira (VCC) é responsável pela alimentação da memória NAND Flash e do bloco de acesso à essa memória (NAND I/O Block).

A segunda entrada de alimentação (VCCQ) é responsável por dois blocos fundamentais desse dispositivo. Primeiramente ela alimenta o bloco de acesso externo, o MMC I/O Block. Esse bloco é responsável pelos níveis de comunicação, e é conveniente que seja alimentado pelo mesmo bloco que fará a interface com o núcleo.

O segundo bloco que ele alimenta é um regulador interno, que fornece uma tensão para o core do dispositivo. Esse regulador interno gera um nível de tensão denominado VCCI (ou VDDI, dependendo da documentação). Como qualquer regulador, ele precisa de um capacitor de filtro que precisa ficar externo ao dispositivo. Esse capacitor possui um valor de, no mínimo, 100nF.

Para o nosso circuito, tanto VCC quanto VCCQ estão ligados na mesma alimentação de VDD_3V3B. Para VCCI, verificamos que foi adotado um capacitor de 2,2uF, o C125.

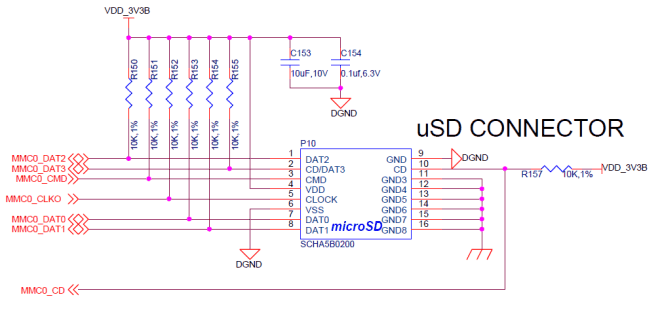

Esse circuito também alimenta diretamente o cartão uSD da plataforma, presente no capacitor P10. Esse cartão segue o mesmo princípio de funcionamento do eMMC, diferenciando em apenas poucos comandos no que se refere ao protocolo. Eletricamente, são praticamente idênticos, exceto pelo eMMC trabalhar com 8 bits de dados, e o uSD trabalhar com 4 bits. Aquém disso, é possível verificar que este circuito é extremamente similar ao do eMMC que vimos anteriormente.

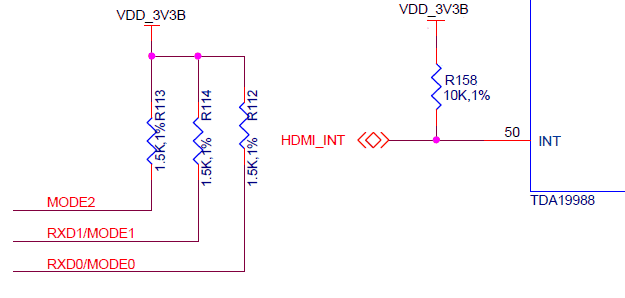

Essa alimentação se apresenta externamente através dos pinos P9.3 e P9.4 do conector de expansão. Também está servindo de referência através de resistores de pull-up para o PHY (R112, R113 e R114) e para a interrupção do HDMI (R158).

Alimentação auxiliar de 3V3 (VDD_3V3AUX)

A alimentação VDD_3V3AUX é fornecida pelo LDO2, que possui uma saída inicial de 3,3V. Tudo indica que o uso de um regulador externo (TL5209, U4) para VDD_3V3B em vez do uso de LDO2 do PMIC é por conta do consumo de corrente. Ele pode fornecer apenas 250mA, metade do regulador usado.

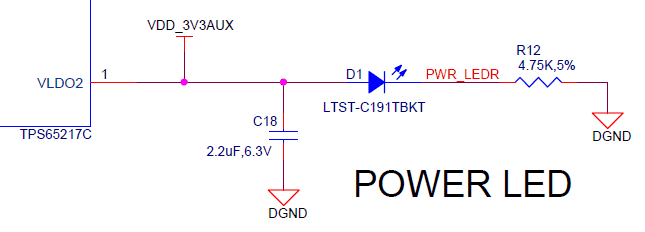

Nas primeiras versões de placa, essa tensão era utilizada como enable para a saída de VDD_3V3B, posteriormente alterada para o próprio VDD_3V3A por questões de sincronismo, como vimos. A única carga presente nele é um LED azul (LTST-C191TBKT), e mesmo esse sofreu alterações. O resistor R12 foi alterado de 820R para 4,75K para diminuir o brilho. O esquema de saída desse circuito é dado conforme segue:

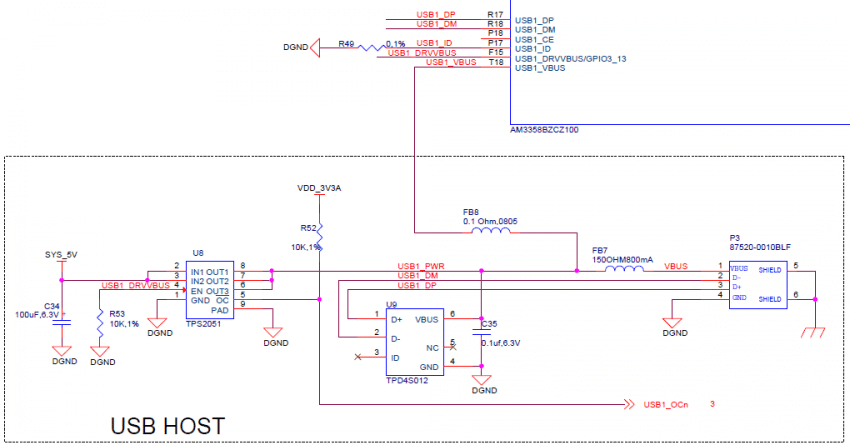

Alimentação da USB Host (USB1_PWR)

O canal USB1_PWR não é exatamente uma saída de um regulador como vimos até então. Mas como trata da alimentação da USB Host do dispositivo, faz todo o sentido ser explicado aqui. Sua alimentação principal vem dos 5V fornecidos por SYS_5V.

Essa alimentação é passada para o conector USB através de um controle chamado TPS2051. Trata-se de um “Power-Distribution Switch”, da Texas Instruments. Ele controla a saída da tensão ou não de acordo com seu pino de Enable. Esse pino possui um resistor de pull-down, o que mantém o dispositivo desabilitado durante a inicialização do sistema. Após essa inicialização, esse pino é controlado por USB1_DRVVBUS, presente no núcleo do GPIO3_13.

Ele também possui um limitador de corrente interno de 500mA. No caso de um curto-circuito ou sobre-corrente, o sistema limita esse valor e indica a informação através de uma saída dreno-aberto. No nosso caso, essa saída é passada para o núcleo através do sinal USB1_OCn, fazendo uso de R52 como resistor de pull-up.

O circuito integrado TPD4012 (U9) é um circuito de proteção ESD de 4 canais, específico para USB. Ele faz a proteção contra qualquer discarga eletrostática que possa acontecer no conector.

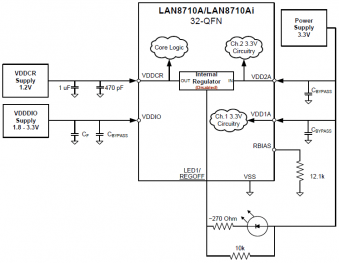

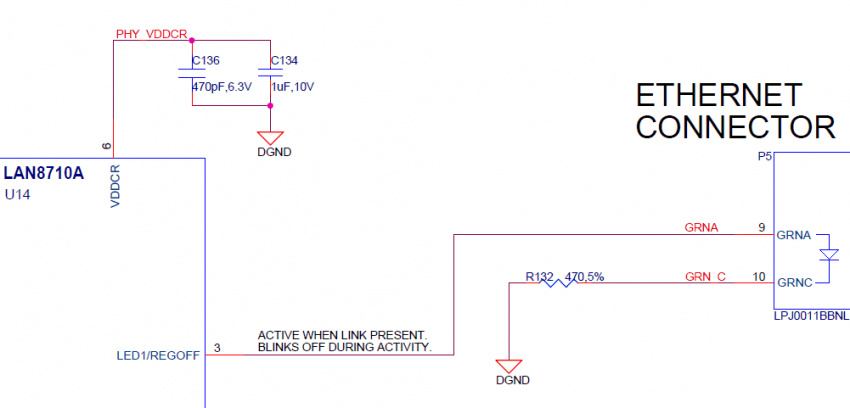

Alimentação da Ethernet (VDD_PHYA)

Trata-se da alimentação dos dispositivos responsáveis pela Ethernet de nossa plataforma, principalmente o LAN8710A (U14). É derivada de VDD_3V3B, passando pelo indutor FB4. Essa tensão também alimenta o ponto central do transformador de rede para RX e TX, através do resistor R137.

Alimentação Interna do LAN8710A (PHY_VDDCR)

Conclusão

Este artigo finaliza a primeira parte do nosso estudo. Verificamos todas a linhas de alimentações, seus limites de correntes, reguladores e filtros. Verificamos quais dispositivos são ligados em cada uma delas e quais as opções que nos são dadas em relação a resistores e componentes.

Vamos continuar nosso trabalho com a BeagleBone Black, agora utilizando o que estudamos como base.

Referência

| LAN8710A | https://ww1.microchip.com/downloads/en/DeviceDoc/8710a.pdf |

| MTFC4GLDEA | https://pdf1.alldatasheet.com/datasheet-pdf/view/526211/MICRON/MTFC4GMVEA-4MIT.html |

| TL5209 | https://www.ti.com/lit/ds/symlink/tl5209.pdf |

| SN74LVC2G241 | https://www.ti.com/lit/ds/symlink/sn74lvc2g241.pdf |

| AM335x Technical Referente Manual | https://www.ti.com/lit/ug/spruh73k/spruh73k.pdf |

| SN74LVC1G06DCK | https://www.ti.com/lit/ds/symlink/sn74lvc1g06.pdf |

| SN74AUC1G74 | https://www.ti.com/lit/ds/sces537d/sces537d.pdf |

| BeagleBone Black BOM | https://github.com/CircuitCo/BeagleBone-Black/blob/master/BBB_BOM.xls |

| ASDMB-24.576MHZ-LC-T | https://www.abracon.com/Oscillators/ASDMB.pdf |

| ECS-2033-24.576-B | https://www.ecsxtal.com/store/pdf/ecs-2025-2033.pdf |

| ISM95-3161BH-24.576 | https://ilsiamerica.com/oscillatordocs/ISM95_Series.pdf |

| LTST-C191TBKT | https://datasheet.octopart.com/LTST-C191TBKT-Lite-On-datasheet-66887.pdf |

| TPS2051 | https://www.ti.com.cn/cn/lit/ds/symlink/tps2051.pdf |