Historicamente, existem métodos preferidos de conversão de energia de CA para CC e de CC para CC. Estes foram definidos por uma variedade de restrições que evoluíram ao longo do tempo. Houve um dia, por exemplo, onde a ‘correção do fator de potência’ era implementada apenas na distribuição CA e uma fonte de alimentação CA/CC poderia felizmente ter um PF de 0,6 ou até menor. Os limites estatutários surgiram por volta de 1982 na Europa. Como resultado, a ‘supressão de harmônicos de rede’, como é chamada com mais precisão, é necessária para alguns equipamentos, como fontes de alimentação com potência nominal superior a 75 W, mas é menor em algumas aplicações, como iluminação. Isso praticamente envolveu a adição de outro estágio de conversão de energia de ‘impulso’ para cada AC/DC, para desgosto dos fabricantes, embora permitisse outros recursos, como entrada universal e tempos de passagem longos. Os primeiros circuitos envolviam um indutor de entrada, chave e diodo retificador e não eram muito eficientes. Da mesma forma, os estágios de conversão DC/DC dentro de um AC/DC acima de 100 W começaram como simples conversores diretos na forma de meias pontes ou pontes completas – relativamente fáceis de entender e implementar, mas com eficiência limitada devido à tecnologia de semicondutores disponível e a natureza ‘hard-switching’ das topologias.

As especificações de desempenho, como o programa de certificação 80 PLUS™ de cerca de 2004, tornaram essas topologias básicas de PFC e conversão DC/DC inviáveis para os níveis de eficiência exigidos: por exemplo, o nível mais alto de ‘Titanium’ requer 96 por cento de eficiência a uma carga percentual de 50 para equipamentos de 230VAC. Novas técnicas, portanto, evoluíram e hoje, uma combinação popular, viável até vários kW, para alta densidade de potência e eficiência é um estágio ‘Totem pole PFC’ (TPPFC) seguido por um conversor ressonante ‘CLLC’.

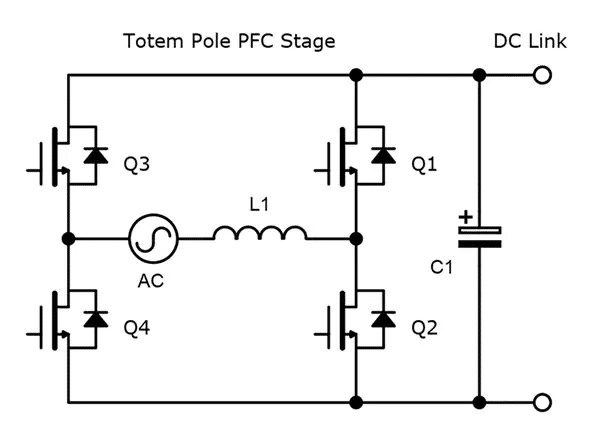

O Estágio Totem Pole PFC

O TPPFC efetivamente elimina o retificador de ponte de entrada em um front-end AC/DC usando chaves semicondutoras como retificadores síncronos (Figura 1). Em potências médias a altas, o circuito é operado no ‘Modo de Condução Contínua’ para manter o pico de corrente gerenciável, resultando em ‘comutação difícil’.

Em uma polaridade principal, Q1 atua como um diodo e Q2 como um interruptor de reforço de alta frequência e, na outra polaridade, as funções são trocadas. Q3 e Q4 atuam como diodos síncronos, fornecendo um caminho para a corrente de linha CA retornar ao fornecimento e podem ser diodos discretos por um custo menor. É claro que existem apenas interruptores no caminho de energia, aqui mostrados como SiC FETs, portanto, as perdas de condução são definidas apenas pelas resistências do dispositivo. Se Si-MOSFETs fossem usados para Q1 e Q2, a recuperação reversa de seus diodos de corpo, que conduzem durante o tempo morto, limitaria a eficiência alcançável. No entanto, com SiC FETs nessas posições, como as peças mais recentes de 750V Gen 4 18mΩ da UnitedSiC (agora Qorvo), uma eficiência de semicondutor de 99,3% pode ser alcançada com saída de 6,6kW, comutada a 75kHz e apenas 8,3W perdidos em cada um dos Q1 e Q2. Isso se deve à resistência líder de mercado e às perdas de recuperação extremamente baixas.

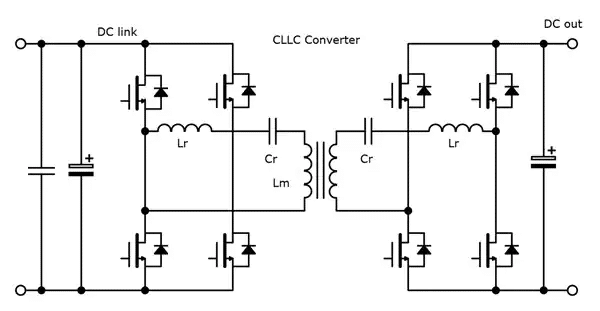

O Conversor CC/CC CLLC

Com uma meta de eficiência geral de 96%, o estágio TPPFC é um ótimo começo. Para o estágio principal de isolamento DC/DC, os benefícios de um conversor ressonante podem ser aproveitados com o popular tipo ‘CLLC’ (Figura 2).

O CLLC é um conversor de frequência variável com uma unidade de ciclo de trabalho de 50 por cento para cada chave e é simétrico, de modo que pode ser usado para conversão bidirecional. A topologia é ressonante, de modo que pode alcançar comutação de tensão zero no primário e corrente zero e comutação de tensão zero no secundário. Em um conversor ressonante, as perdas de comutação são muito baixas e a recuperação do diodo do corpo não é um problema, então a frequência pode ser aumentada para minimizar o tamanho magnético. No entanto, há um limite para isso ser influenciado pela capacitância de saída do dispositivo, que dita o tempo mínimo ‘morto’ e a faixa de operação. Novamente, SiC FETs são uma escolha ideal, com a melhor figura de mérito para capacitância de saída específica e resistência no mercado em altas e baixas temperaturas, bem como uma queda de tensão direta de diodo de corpo muito baixa, resultando em excelente eficiência. Por exemplo, em 300kHz, 6,6kW, as mesmas peças UnitedSiC Gen 4 usadas no estágio PFC de exemplo produzem 99,8% de eficiência de semicondutor. Um benefício adicional dos SiC FETs é o fácil acionamento do portão de 0 a 12 V.

A UnitedSiC desenvolveu uma gama de peças SiC FET de 750 V Gen 4 com pacotes opcionais e resistências de modo que os projetistas tenham uma ampla escolha para atender às suas metas de desempenho e orçamentos. Todas as opções podem ser exploradas com o FET-Jet Calculator™ online da empresa, que fornece resultados instantâneos de desempenho para SiC FETs em uma ampla variedade de topologias selecionáveis, incluindo TPPFC e CLLC. A potência dissipada, os aumentos de temperatura e os níveis de tensão dos componentes são indicados, com o usuário capaz de especificar as condições de operação elétrica e térmica junto com o efeito de paralelismo de várias peças.

Temos as melhores topologias e switches agora? Com eficiências de estágio agora apenas uma pequena fração de um por cento longe de 100%, estamos bem próximos.

Artigo escrito por Qorvo e publicado no blog da Mouser Electronics: SiC FETs in Latest Power Conversion Topologies

Traduzido pela Equipe Embarcados. Visite a página da Mouser Electronics no Embarcados

(*) este post foi patrocinado pela Mouser Electronics.