Jan Gray publicou um artigo bem interessante, comparando o número de processadores RISC de 32-bits que cabiam em um FPGA de 1995 e quantos cabem hoje.

O processador, chamado de J32, possui uma arquitetura RISC clássica com instruções com três operações, pipeline de quatro estados (fetch, register read, execute, writeback) e um registrador operand file de 32 bits.

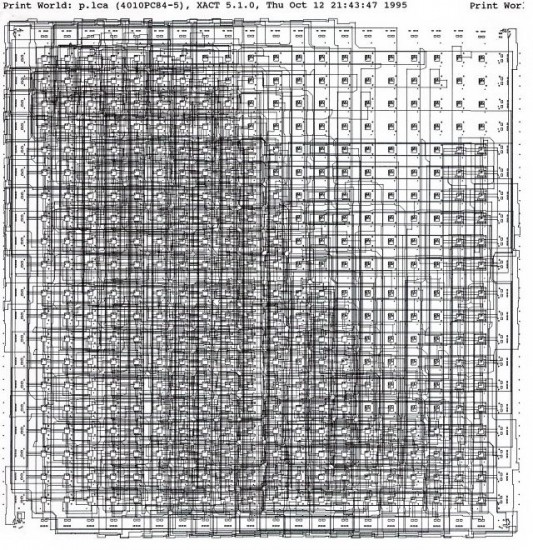

Em 1995 esta arquitetura ocupava um FPGA Xilinx XC4010PC84-5 FPGA por completo, ou seja, 800 Look up Tables (LUT) de quatro entradas. O layout ficou assim:

Hoje, 13 anos depois, o mesmo processador J32 sintetizado em uma Virtex-7 ocupa apenas 0,1% do chip. Com 433,000 LUTS de 6 entradas é possível sintetizar 1.000 destes processadores em um único chip.

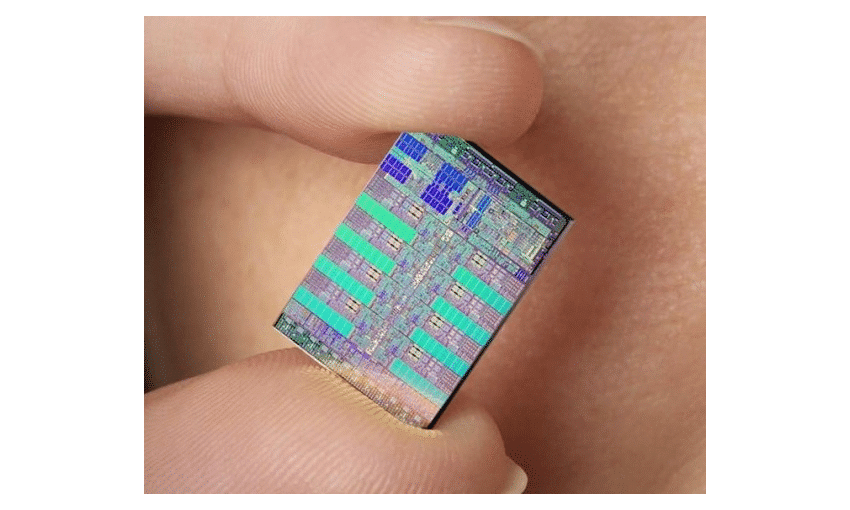

O layout atual ficou assim:

Em outras palavras, nos ultimos 18 anos, a lei de Moore nos levou de 1.000 LUTs por FPGA para 1.000 CPUs de 32-bits por FPGA. Com a maior Virtex (4,4 milhões de células lógicas), conseguiremos atingir 10.000 processadores de 32 Bits com a interconexão em um único FPGA em um futuro próximo.