O FPGA é uma tecnologia muito interessante, com capacidade de fazer desde pequenas lógicas, até processadores inteiros (vide o artigo AHMES, do Fábio Pereira). No entanto, ainda é pouco difundida no Brasil. Começar com essa tecnologia pode parecer algo complicado, mas de fato não é. Ferramentas gratuitas e documentos sobre o assunto podem ser encontrados sem muitas dificuldades nos sites dos fabricantes. No entanto, aquele primeiro empurrãozinho para a pessoa fazer sua primeira brincadeira com lógica programável pode ajudar, e muito. Essa foi a motivação deste artigo. Você terá seu primeiro contato com o ambiente de desenvolvimento ISE Design Suite, de maneira a dar o pontapé inicial para você se desenvolver sozinho. O que vamos fazer aqui é simular uma porta AND, e nada mais.

Já tivemos dezenas de outros artigos aqui no Embarcados, como por exemplo:

- Tutorial de Verilog – Operadores – Por: Thiago Lima

- Tutorial de Verilog – Conversor BCD para 7 Segmentos – Por: Thiago Lima

- Tutorial de Verilog – Operadores Lógicos e Aritméticos – Por: Rodrigo Pereira

No entanto, destaco um artigo em especial: Tutorial de Verilog – O Primeiro projeto com Quartus, por Thiago Lima. Nesse artigo foi apresentado passo a passo como criar seu primeiro projeto com o Quartus II, da Altera. Aqui faremos igual, só que diferente. Você fará seu primeiro projeto com o ISE, da Xilinx.

Criando Seu Projeto no ISE Web Pack Suite

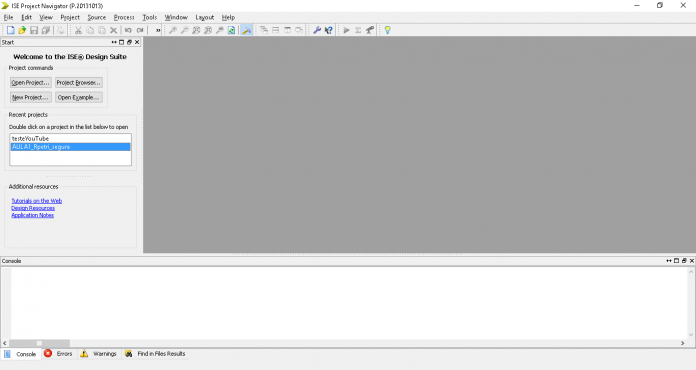

A ferramenta que vamos utilizar se chama ISE Design Suite na versão 14.7, que pode ser encontrada no site da Xilinx. A versão que estamos utilizando é a Web Pack, que pode ser baixada gratuitamente. No entanto, é necessário fazer um cadastro e baixar um arquivo de licença para o sistema funcionar.

Assim que o sistema carrega, apresenta uma janela de ambiente de desenvolvimento. Há sempre uma janela com dicas quando o programa inicializa. O que vamos fazer aqui é criar um novo projeto, então nada mais simples que File->New Project.

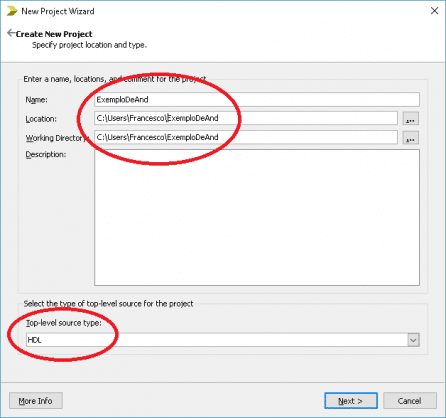

A janela New Project Wizard irá abrir. Nela vamos indicar o nome do projeto e o diretório de trabalho. Há uma seleção para o tipo de arquivo a ser desenvolvido, mas vamos deixar em HDL.

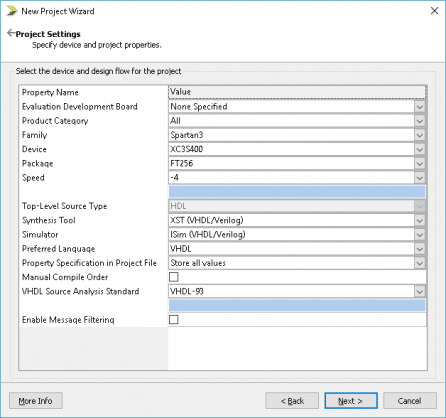

Na janela seguinte, faremos a seleção do dispositivo a se trabalhar. Como vamos trabalhar com simulação e com algo muito simples, qualquer dispositivo atende. No entanto, deixaremos a configuração como Spartan 3. Se você for continuar a desenvolver a partir desse artigo, este dispositivo atenderá a praticamente tudo mais o que lhe possa ser necessário.

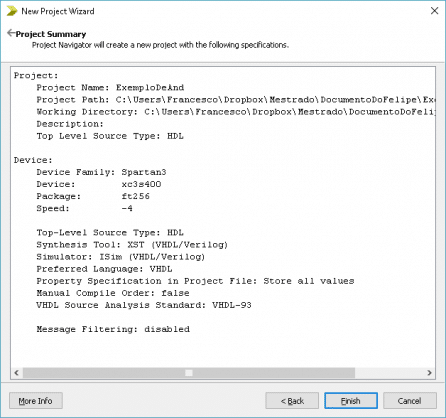

Por último, apenas um sumário é apresentado com as características iniciais do seu projeto.

Uma vez terminada esta etapa, o nosso ambiente já está com o projeto aberto.

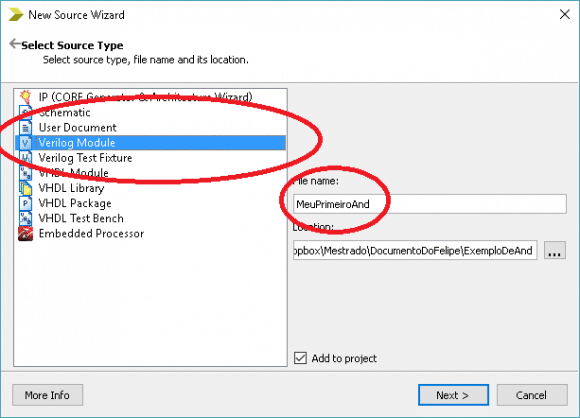

Agora vamos adicionar um novo módulo ao sistema. Basta clicar com o botão direito do Mouse sobre nosso projeto e adicionar um novo arquivo fonte.

Vamos criar um módulo Verilog. Não é obrigatório, tão pouco mais ou menos recomendado o uso do Verilog. Apenas vamos seguir por ele. Se você se sente confortável com VHDL, pode faze-lo. Seguiremos, então selecionando Verilog Module e escolhendo o nome do arquivo, MeuPrimeiroAnd parece bom.

Em seguida, adicionaremos os IOs necessários para esse módulo. Como trata-se de uma porta AND, nada mais clássico que duas portas, A e B, e uma saída S. Lembre-se de certificar-se das direções.

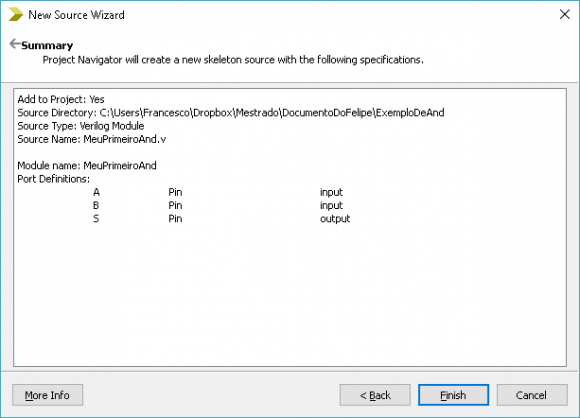

Por último, é apresentado um sumário com suas opções. Agora o arquivo MeuPrimeiroAnd.v foi adicionado à árvore de projetos. O fonte criado automaticamente é apresentado logo abaixo.

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 23:43:17 09/18/2016

// Design Name:

// Module Name: MeuPrimeiroAnd

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module MeuPrimeiroAnd(

input A,

input B,

output S

);

endmodule

Perceba que os IOs foram definidos no código, mas não existe implementação nenhuma. Vamos, então, à difícil tarefa de criar uma porta AND. Adicione a seguinte linha no código:

assign S = A & B ;

Para ter mais detalhes sobre os operadores do Verilog, acesse este ótimo artigo do Thiago Lima. Seu módulo ficará assim:

module MeuPrimeiroAnd(

input A,

input B,

output S

);

assign S = A & B ;

endmodule

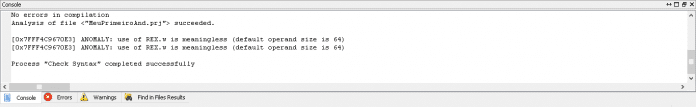

Salve o código para verificar a sintaxe. Para isso, abra a árvore Synthesize – XST e clique com o botão direito em Check Syntax. Selecione Run, isso iniciará o processo de checagem de sintaxe.

Você poderá acompanhar o processo pela janela Console. Lá, você encontrará o resultado. Se fez o procedimento corretamente até aqui, você verá Process Check Syntax completed successfully.

Simulando Sua Porta AND no ISE

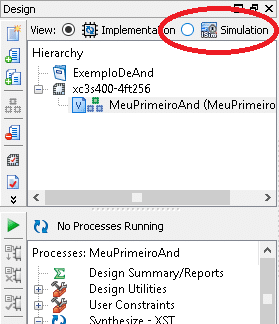

Agora vamos iniciar o processo de simulação do módulo que criamos. Para fazer isso, primeiro precisamos mudar o modo de visualização de Implementação para Simulação. Para fazer isso, basta clicar no objeto Simulation.

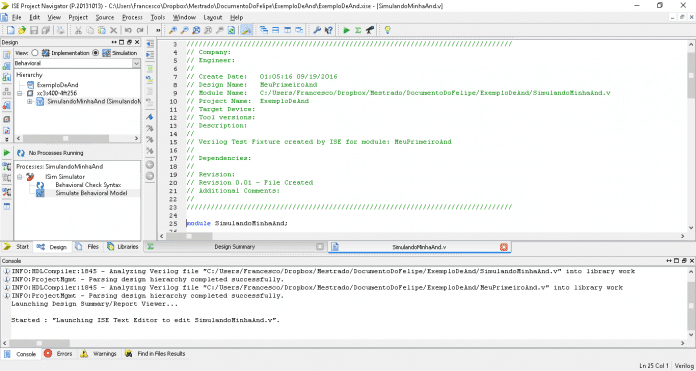

Precisaremos adicionar um novo arquivo fonte no nosso projeto, o Verilog Test Fixture. O procedimento é exatamente o mesmo que fizemos para criar nosso Verilog Module. Vamos dar o nome de SimulandoMinhaAnd e clicar em Next.

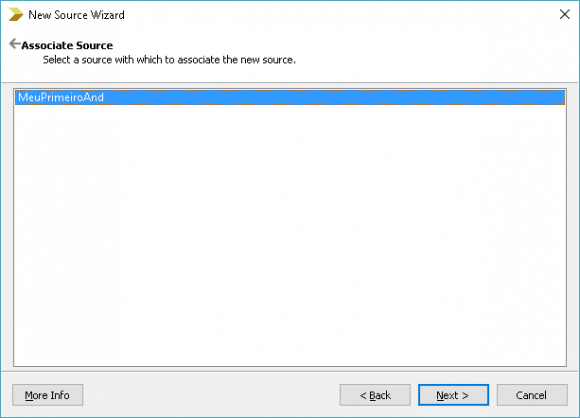

Em seguida, o ISE lhe perguntará quais os módulos você deseja testar. Como nós criamos apenas um módulo, teremos apenas ele como opção. Vamos, então, seguir com Next.

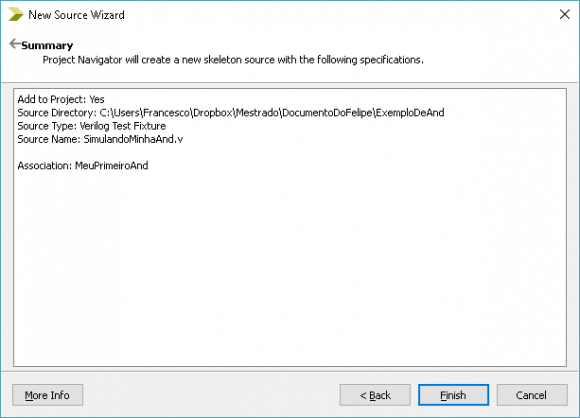

Por último, como em todos os casos, uma janela de sumário é apresentada com as características de nossa criação.

Agora, um novo arquivo foi adicionado ao projeto. Ele controla todo o processo de testes, e precisamos definir como esse stript vai funcionar. O fonte automaticamente criado se apresenta da seguinte forma:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 01:05:16 09/19/2016

// Design Name: MeuPrimeiroAnd

// Module Name: C:/Users/Francesco/Dropbox/Mestrado/DocumentoDoFelipe/ExemploDeAnd/SimulandoMinhaAnd.v

// Project Name: ExemploDeAnd

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: MeuPrimeiroAnd

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module SimulandoMinhaAnd;

// Inputs

reg A;

reg B;

// Outputs

wire S;

// Instantiate the Unit Under Test (UUT)

MeuPrimeiroAnd uut (

.A(A),

.B(B),

.S(S)

);

initial begin

// Initialize Inputs

A = 0;

B = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

endmodule

O que nos interessa está entre initial begin e end. Perceba que nossas duas entradas estão definidas, e recebem valores padrão 0. O valor apresentado com # é o tempo que será aguardado, nesse caso #100 representa 100ns. Como trata-se de uma simulação, o tempo não nos fará diferença.

Adicione os outros casos de teste, onde as entradas AB serão 01, 10 e 11. É interessante realizar essas mudanças a cada passo de tempo. Dessa forma, a cada nova composição de A e B, vamos adicionar um passo de 100ns. Nosso arquivo ficará assim:

module SimulandoMinhaAnd;

// Inputs

reg A;

reg B;

// Outputs

wire S;

// Instantiate the Unit Under Test (UUT)

MeuPrimeiroAnd uut (

.A(A),

.B(B),

.S(S)

);

initial begin

// Initialize Inputs

A = 0;

B = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

A = 0;

B = 1;

#100;

A = 1;

B = 0;

#100;

A = 1;

B = 1;

#100;

A = 0;

B = 0;

#100;

A = 0;

B = 1;

#100;

A = 1;

B = 0;

#100;

A = 1;

B = 1;

#100;

end

initial begin

$monitor("AB[%d%d] S=[%d]\n" , A , B , S ) ;

end

endmodule

Perceba que adicionamos duas vezes o ciclo de entrada, pois queremos deixar bastante evidente o resultado da nossa porta AND. Também é importante verificar a linha, $monitor. Ela irá apresentar o resultado de cada passo no Console, de forma a acompanharmos os dados.

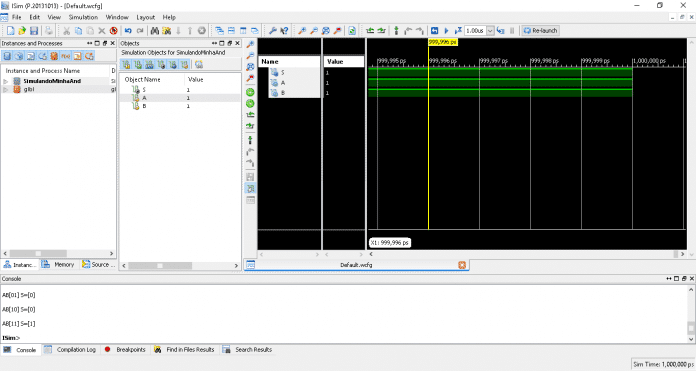

Vamos, então, abrir a árvore ISim Simulator e clicar com o botão direito em Simulate Behavioral Model, selecionando a opção Run.

Da mesma forma que vimos anteriormente, você poderá acompanhar o andamento pela janela Console. Estando tudo correto, o sistema automaticamente abrirá o software ISim, responsável pela simulação.

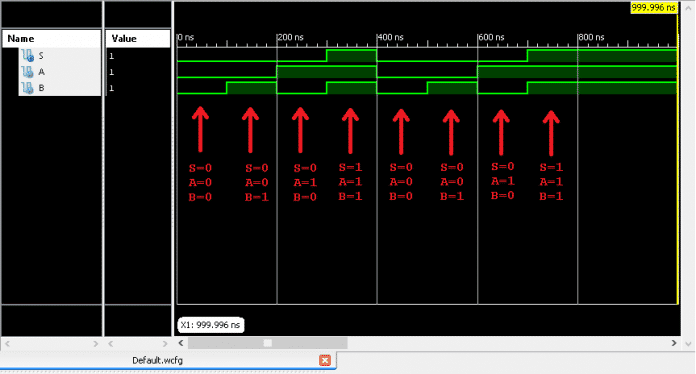

Perceba que este software também possui a janela de console, e nele você vê o resultado da formatação feita em $monitor. Agora, para verificar a forma de onda, clique no ícone Zoom to Full View.

Aqui vemos toda a forma de onda criada, e o resultado de nossa porta AND. Perceba que S apenas é 1 quando A e B são 1 simultaneamente, conforme esperávamos.

A partir daqui você pode evoluir os módulos, desenvolver lógicas complexas, e evoluir os estudos dentro das tecnologias de FPGA. Boa sorte!

Referências

ISE Web Pack Design Software – Xilinx

Xilinx ISE Simulation Tutorial – YouTube

Step by Step Simulation ISE+MATLAB – Vihang Naik