No artigo sobre kits de desenvolvimento com FPGA de André Prado publicado aqui no Embarcados, ele citou uma placa que talvez seja uma das que mais vale a pena comprar para aprender a programar FPGA, utilizando, claro, Verilog e VHDL. Essa placa é a DE0-Nano, fabricada pela Terasic e desenvolvida em parceria com a Altera.

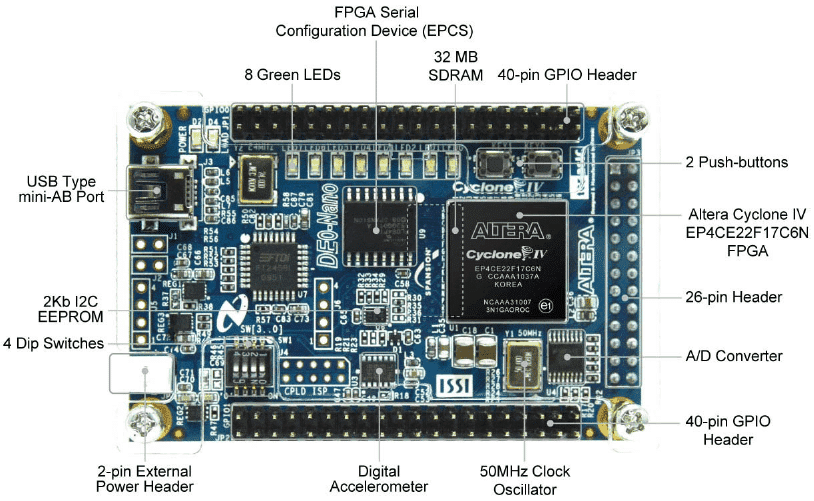

Essa placa conta com FPGA Altera Cyclone IV EP4CE22F17C6N (com 22320 elementos lógicos), 32 MB de SDRAM, 2 Kb EEPROM, e uma memória serial de 64 KB utilizada para configuração. Ela não precisa de nenhum dispositivo externo para ser programada. Basta conectar a placa à USB e o PC a alimenta e a reconhece, caso os software da Altera (testamos o Quartus II 13.0 e 14.0) estejam instalados no PC. Isso é o que eles chamam de “On-board USB-Blaster circuit for programming”. A IDE é grátis na versão WEB Edition e pode ser baixada no link.

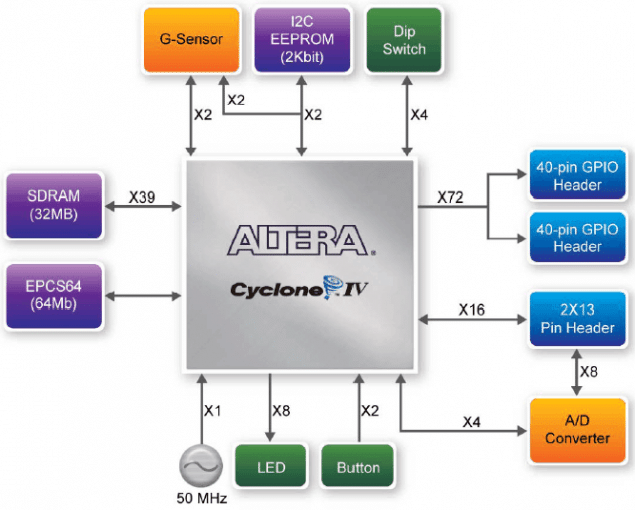

Alem do FPGA, a placa conta com:

- 8 Leds, 2 pushbuttons e 4 dip switches, cada um com dois estados, ótimos para experiências rápidas e validação de conceitos;

- 1 Acelerômetro de três eixos com resolução de 13 bits da Analog Devices ADXL345;

- Conversor A/D da antiga National Semiconductor (agora Texas Instruments) ADC128S022 de 8 canais, e de 12-bits com taxa e conversão de 50 Ksps a 200 Ksps;

- Pinos de expansão (72 I/Os), além de pinos de alimentação 5V, 3.3V e de referência terra;

- Memória SDRAM de 32MB;

- Memória EEPROM de 2Kb I2C;

- Memória Flash Spansion EPCS64 para fins de programação;

- Sistema de clock on-board com um oscilador dedicado de 50 MHz;

- Alimentação por um conector USB tipo mini-AB ou por um header externo.

Veja o diagrama de blocos da placa na figura 1 e as vistas superior e inferior da placa nas figuras 2 e 3, respectivamente.

Saiba mais

Para aprender mais sobre FPGA confira os artigos de André Prado neste site. Selecionei alguns como referência:

Referências

ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE0-Nano/DE0_Nano_User_Manual.pdf

Fonte das Imagens: ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE0-Nano/DE0_Nano_User_Manual.pdf

Para quem pretende usar este hardware e ja tem familiaridade com HDL este projeto opensource em anexo ja tem uma plataforma para a DE0 nano e outras(Xilinx e Altera independente da amarracao do fabricante!). Com um processador RISC opensource e implementacao de barramento opensource WISHBONE + controlador de memoria:

https://m-labs.hk/gateware.html

https://github.com/m-labs/migen/tree/master/mibuild/platforms

https://github.com/m-labs/migen/blob/master/mibuild/platforms/de0nano.py

https://github.com/m-labs/misoc

Sou leigo no assunto e gostaria de saber se para desenvolver projetos com essa placa, por exemplo, a IDE seria o NIOS II ou o Quartus II Web Edition Software?

Olá Eder.

O software para FPGAs Altera é o Quartus II. Nele está concentrado tudo da parte de FPGA.

A parte do NIOS2-IDE seria para desenvolver software para o NIOS2 em C, como se fosse um processador qualquer.

Abs

Obrigado André.

Tanto o Quartus como o NIOS são pagos?

O Quartus II tem uma versão gratuita que pode ser usada para fazer produtos sem problemas, o diferencial para a versão paga é o tempo de compilação, alguns recursos a mais e alguns IPs.

O NIOS2 é gratuito na configuração “Economy”, que seria equivalente a um M0 talvez.

Já nas outras duas versões mais tops ele é pago. Ai você compra o IP e pode botar nos produtos sem problemas.

Você pode desenvolver absolutamente tudo com a versão gratuita (Aí o NIOS2 nas versões pagas se auto destrói em 30 minutos com a placa ligada ao cabo).

Abraço

Obrigado!

Oi Eder, com a versao do Quartus da’ pra fazer tudo pra fins didaticos.

Quantos LE’s eu preciso para começar a mexer com softcores?

É que estou desenvolvendo uma placa FPGA e não tenho acesso a BGA no momento, sendo que estou limitado a chips de 8k ou 10k.

Cordialmente.

Olá Luciano, no caso da Altera aqui tem uma tabela:

https://www.altera.com/literature/ds/ds_nios2_perf.pdf

8k da e sobra para mexer com o NIOS2 (softcore da Altera) mesmo na versão mais completa.

Você também pode desenvolver seu próprio softcore ou usar outros, como por exemplo o Z80 do opencores:

https://opencores.org/project,t80

https://opencores.org/project,z80soc

Pode baixar o código e sintetizar e ver quanto de lógica utilizaria.

Abraço

Grato.

Verdade, dá e sobra. Vou fazer o projeto com o EP4C10. Com os 10k desse chip dá para fazer até algo multicore ou sobra espaço para algoritmos concorrentes.