Em um tutorial passado, Andre Prado e eu apresentamos a ferramenta Modelsim, que possibilita simular o comportamento de circuitos descritos em linguagens de descrição de hardware, tais como VHDL e Verilog. Para acessar o artigo sobre ModelSim. O exemplo apresentado foi simples, mas possivelmente já serviu de ponto de partida para o aprendizado de linguagens de descrição de hardware, pois possibilita testar os conceitos sem a utilização de um FPGA físico. Essa série de tutoriais dará mais um passo no mundo da simulação, e de quebra seremos apresentados ao processador softcore Altera Nios II. Neste tutorial apresentarei a Arquitetura do Altera Nios II e, no próximo artigo, falarei sobre Simulação do Nios II no Modelsim.

Arquitetura Altera Nios II

O Nios II é um processador softcore RISC de 32 bits com arquitetura Harvard desenvolvido pela Altera. Mas o que isso significa? Um processador softcore é uma implementação de um processador descrito em linguagem de hardware, que pode ser customizado e sintetizado em um FPGA ou ASIC. Uma vantagem evidente no uso de softcores está na flexibilidade pois possibilita a fácil conexão com outros periféricos, alteração do conjunto de instruções e, o mais evidente, alteração das estruturas internas do processador, tais como tamanho da memória cache, priorização de interrupções, dentre outros. Um processador com arquitetura Harvard é um processador que tem memórias separadas para alocar dados e instruções.

O Altera Nios II apresenta as seguintes características:

- Processador RISC com pipeline;

- 32 registradores de propósito geral;

- 3 formatos de instrução;

- Instruções de 32bits;

- Endereçamento de 32bits;

- Cache de dados e de instruções separados com tamanhos configuráveis;

- Memória on-chip;

- Branch Prediction;

- 32 interrupções priorizáveis;

- On-chip hardware (Multiplicaçãos, shift, rotate…);

- Memory Management Unit (MMU);

- Memory Protection Unit (MPU);

- Instruções customizadas em hardware;

- Debug utilizando JTAG;

A Altera disponibiliza o softcore em 3 “sabores”:

- Fast: voltado para o desempenho (maior consumo de espaço no FPGA);

- Standard: equilíbrio entre consumo de lógica e velocidade;

- Economy: voltado para a economia de lógica.

É interessante notar que o código compilado para a arquitetura Altera Nios II é compatível com as três implementações possíveis do processador.

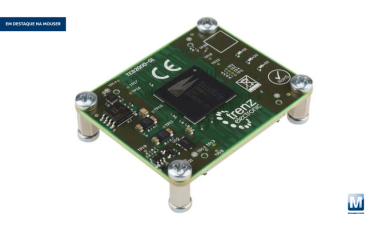

O Nios é livre de Royalties e não precisa nem de licença comercial do Quartus II para que você possa embarcá-lo em suas aplicações, para o caso da versão Economy. O restante das versões necessita que você tenha uma licença comercial do Quartus II para distribuir o Nios embarcado em algum produto. A figura a seguir apresenta a arquitetura de um design de referência utilizado em muitos dos kits de FPGAs da Altera.

A figura 1 apresenta dois tipos de componentes: implementados em linguagem de descrição de Hardware (“On-chip” – em laranja) e externos, implementados em CIs presentes nas placas dos kits (“off-chip” – em azul). Pela figura 1, pode-se notar que o Processador Softcore Altera Nios II se comunica com os demais componentes por meio das conexões criadas pelo Qsys (Qsys Interconnect). O Qsys é uma ferramenta desenvolvida pela Altera para criação de SOPCs (System on a Programmable Chip).

Referências