Introdução

Neste tutorial vamos aprender a trabalhar com o ModelSim no terminal Linux. Usar os comandos que esta ferramenta disponibiliza para compilar e criar bibliotecas de trabalho para projetos de circuitos digitais, da descrição RTL ao test bench.

Como todo projeto, projetos de hardware requer um grande esforço de depuração, isto é, o projeto é modificado várias vezes até atender as especificações desejadas. Dessa forma, é sempre bem vindo um ambiente de desenvolvimento “limpo” e rápido para se trabalhar. Pensando nisso, o ModelSim, via terminal Linux, juntamente com um bom editor de texto, satisfazem essa demanda.

Instalação do ModelSim no Terminal Linux

Você pode adquirir as versões gratuitas (Students) do ModelSim pelo site do fabricante Mentor Graphics a partir deste link, ou pelo site da Altera (requer criação de conta) neste link. Neste tutorial foi usada a versão disponibilizada pela Altera. É importante lembrar de escolher a opção para plataforma Linux.

Após o download, podemos prosseguir para sua instalação. Para distribuições Linux 64 bits é necessário instalar 3 bibliotecas que dão suporte para aplicações 32 bits, são estas: libc6:i386, libncurses5:i386 e libstdc++6:i386. Além disso, deve-se adicionar a arquitetura i386. Para executar essas ações basta abrir um terminal e executar os passos abaixo. Se você está usando alguma distribuição 32 bits, ignore esta etapa.

sudo dpkg --add-architecture i386 sudo apt-get update sudo apt-get install libc6:i386 libncurses5:i386 libstdc++6:i386

O próximo passo é executar o instalador do ModelSim em modo superusuário (root), dando acesso ao software para todos os usuários do sistema (opcional, mas recomendado). No terminal navegue até o arquivo baixado e execute:

sudo ./ModelSimSetup-15.1.0.185-linux.run

Caso o ModelSim não esteja como executável, faça-o:

chmod +x ModelSimSetup-15.1.0.185-linux.run sudo ./ModelSimSetup-15.1.0.185-linux.run

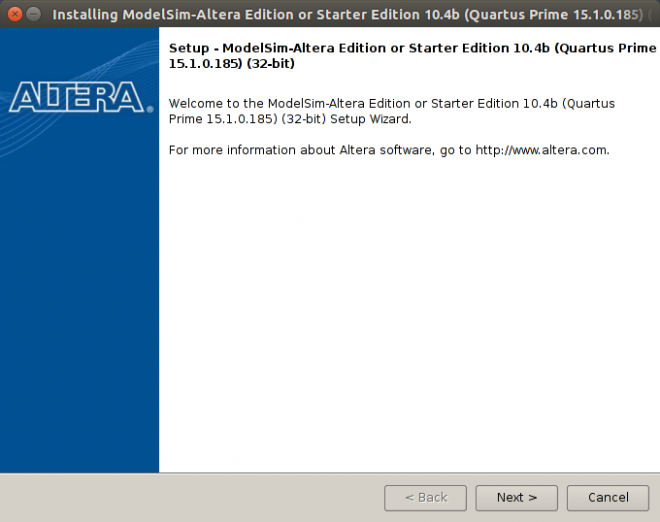

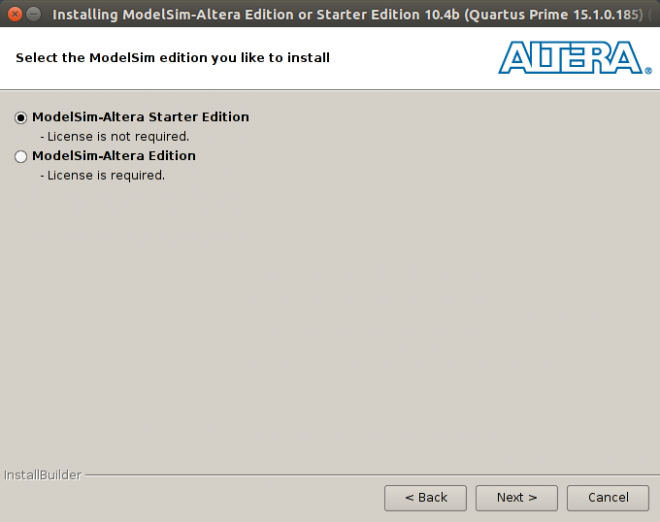

Isso fará com que a interface de instalação seja aberta, então basta seguir os passos ilustrados nas figuras seguintes, configurando e clicando em Next.

Na próxima tela (figura 4), o diretório /opt/altera/15.1 foi escolhido. Este diretório geralmente é usado para instalar programas de terceiros (programas que não estão disponíveis nos repositórios oficiais da distribuição). Essa escolha é opcional, mas recomendo para que suas atividades fiquem compatíveis com a do tutorial.

Nas próximas telas basta continuar escolhendo Next e aguardar o fim da instalação.

Configuração

Para que os comandos do ModelSim sejam encontrados pelo sistema é necessário alterar a variável de ambiente PATH. De forma simples e objetiva, a variável PATH define os caminhos onde o interpretador vai buscar os comandos demandados. Para isso, execute os seguintes passos:

sudo gedit /etc/bash.bashrc

Na última linha do arquivo bash.bashrc você acrescentará mais um caminho para a variável PATH. Caso você tenha escolhido o mesmo caminho que o tutorial, basta copiar e colar a seguinte linha abaixo, se não coloque o diretório equivalente que você escolheu.

export PATH=${PATH}:/opt/altera/15.1/modelsim_ase/linuxaloem

Reinicie o terminal para aplicas as alterações.

Laboratório

Neste tópico vamos fazer um Hands-On demonstrando como gerar um ambiente de desenvolvimento que nos possibilitará compilar e simular circuitos digitais, usando a ferramenta instalada. Nosso alvo será desenvolver o circuito Meio Somador em VHDL. As etapas serão comentadas e dessa forma teremos uma metodologia do uso da ferramenta, dando base de conhecimento para quaisquer aplicações futuras.

1. Abra o terminal, escolha um diretório de trabalho, por exemplo /home/user (ou simplesmente ~) e crie os seguintes diretórios para o projeto.

cd ~ mkdir -p HALF_ADD/vhd HALF_ADD/bench HALF_ADD/libs/lib_VHDL HALF_ADD/libs/lib_BENCH HALF_ADD/config HALF_ADD/doc

Um caminho alternativo é criar um arquivo de texto, colocar os comandos para a criação destes diretórios, gerar um executável deste arquivo e executar.

Após esta ação você terá criado 5 pastas:

- /vhd: Conterá os circuitos desenvolvidos em vhd;

- /bench: Conterá os arquivos de test bench;

- /libs: Conterá as bibliotecas de trabalho;

- /config: Conterá Script que configurará variáveis de ambiente;

- /doc: Sugestão para colocar arquivos como Datasheet, Manuais, etc.

2. Com os diretórios criados, vamos ao próximo passo que é a criação de um Script para “setar” variáveis de ambiente que nos auxiliarão. No diretório HALF_ADD/config crie o arquivo config_RTL, isto é:

cd ~/HALF_ADD/config gedit config_RTL

Copie, cole e salve o seguinte Script:

#!bin/bash

export PATH_WORK=~/HALF_ADD

printf "\nPATH_WORK (caminho da pasta de trabalho) = \n%s\n\n" "$PATH_WORK"

export MODELSIM="${PATH_WORK}/config/modelsim.ini"

printf "\nMODELSIM = \n%s\n\n" "$MODELSIM"

Este Script define a variável PATH_WORK para indicar o caminho base do diretório de trabalho, e a variável MODELSIM define onde será criado o arquivo modelsim.ini, sendo que podemos modificá-lo para ajustar o ModelSim para o projeto corrente. Execute-o fazendo:

source config_RTL

3. Desenvolvimento do Projeto

Na diretório /vhd vamos desenvolver os circuitos do projeto: PORTA_AND.vhd, PORTA_XOR.vhd e HALF_ADD.vhd. Como sugestão de editor, eu recomendo o emacs.

library IEEE;

use IEEE.std_logic_1164.all;

entity PORTA_AND is

port (

A : in std_logic;

B : in std_logic;

S : out std_logic);

end entity PORTA_AND;

architecture RTL of PORTA_AND is

begin -- architecture RTL

S <= A and B;

end architecture RTL;

Vamos aos comandos do ModelSim para compilarmos o circuito e criar a biblioteca de trabalho deste projeto. Primeiro crie o arquivo compil_VHDL:

gedit compil_VHDL

Adicione a seguinte sequência de comandos nesse arquivo:

vdel -lib ${PATH_WORK}/libs/lib_VHDL -all

vlib ${PATH_WORK}/libs/lib_VHDL

vmap lib_VHDL ${PATH_WORK}/libs/lib_VHDL

vcom -work lib_VHDL PORTA_AND.vhd

Crie um executável e execute-o:

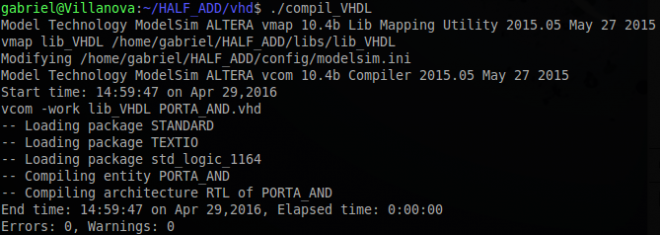

chmod +x compil_VHDL ./compil_VHDL

Você terá como saída no terminal:

Interpretando os comandos:

- vdel: Remove uma unidade de design ou remove a biblioteca selecionada (por default a biblioteca será a work). No nosso caso ele exclui a biblioteca lib_VHDL, fazemos isso para não sobrescrever a biblioteca atualizando-a sempre que executamos o Script;

- vlib: Cria uma biblioteca de projeto no diretório especificado. No nosso caso, veja que ele criará a lib_VHDL;

- vmap: Define um mapeamento entre um nome da biblioteca (lib_VHDL) e um diretório, modificando o arquivo modelsim.ini;

- vcom: Compila o projeto VHDL especificado. A opção -work especifica que a lib_VHDL será a biblioteca a ser usada.

OBS: Se você estiver trabalhando com Verilog ou SystemVerilog, basta substituir o comando vcom por vlog.

O próximo circuito é PORTA_XOR.vhd:

library IEEE;

use IEEE.std_logic_1164.all;

entity PORTA_XOR is

port (

A : in std_logic;

B : in std_logic;

S : out std_logic);

end entity PORTA_XOR;

architecture RTL of PORTA_XOR is

begin -- architecture RTL

S <= A xor B;

end architecture RTL;

Para adicionar esse circuito na compilação, basta adicionar vcom indicando as dependências corretas e reexecutar. O Script compil_VHDL ficará da seguinte forma:

vdel -lib ${PATH_WORK}/libs/lib_VHDL -all

vlib ${PATH_WORK}/libs/lib_VHDL

vmap lib_VHDL ${PATH_WORK}/libs/lib_VHDL

vcom -work lib_VHDL PORTA_AND.vhd

vcom -work lib_VHDL PORTA_XOR.vhd

Por fim, escrevemos o circuito principal HALF_ADD.vhd que usará os outros circuitos.

library IEEE;

use IEEE.std_logic_1164.all;

entity HALF_ADD is

port (

A : in std_logic;

B : in std_logic;

C : out std_logic;

S : out std_logic);

end entity HALF_ADD;

architecture RTL of HALF_ADD is

component PORTA_AND is

port (

A : in std_logic;

B : in std_logic;

S : out std_logic);

end component PORTA_AND;

component PORTA_XOR is

port (

A : in std_logic;

B : in std_logic;

S : out std_logic);

end component PORTA_XOR;

begin -- architecture RTL

X0 : PORTA_XOR port map (A,B,S);

A0 : PORTA_AND port map (A,B,C);

end architecture RTL;

Mais uma vez, adicionamos o comando vcom para o HALF_ADD.vhd.

vdel -lib ${PATH_WORK}/libs/lib_VHDL -all

vlib ${PATH_WORK}/libs/lib_VHDL

vmap lib_VHDL ${PATH_WORK}/libs/lib_VHDL

vcom -work lib_VHDL PORTA_AND.vhd

vcom -work lib_VHDL PORTA_XOR.vhd

vcom -work lib_VHDL HALF_ADD.vhd

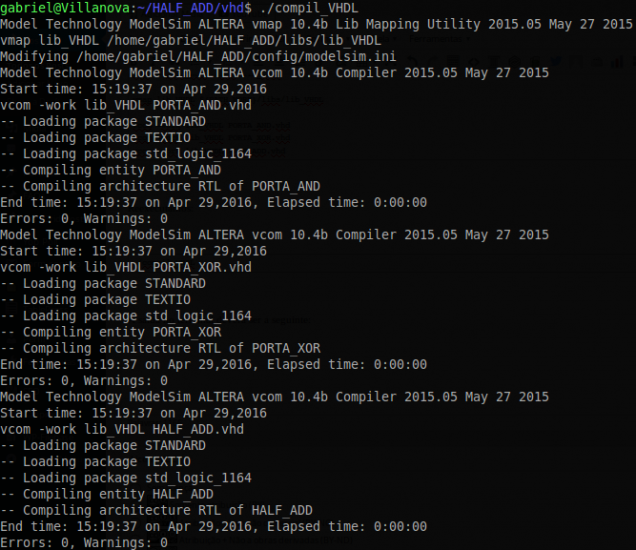

Reexecutamos:

./compil_VHDL

A saída no terminal deverá ser a seguinte:

4. Criação de test bench

No diretório /bench abrimos um arquivo TB_HALF_ADD.vhd onde escreveremos o test bench do nosso Meio Somandor (HALF_ADD).

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

library lib_VHDL;

use lib_VHDL.HALF_ADD;

entity TB_HALF_ADD is

end entity TB_HALF_ADD;

architecture RTL of TB_HALF_ADD is

component HALF_ADD is

port (

A : in std_logic;

B : in std_logic;

C : out std_logic;

S : out std_logic);

end component HALF_ADD;

signal sig_A : std_logic;

signal sig_B : std_logic;

signal sig_C : std_logic;

signal sig_S : std_logic;

begin -- architecture RTL

H0: HALF_ADD port map (sig_A,sig_B,sig_C,sig_S);

process

begin

sig_A <= '0';

sig_B <= '0';

wait for 10 ns;

sig_A <= '0';

sig_B <= '1';

wait for 10 ns;

sig_A <= '1';

sig_B <= '0';

wait for 10 ns;

sig_A <= '1';

sig_B <= '1';

wait for 10 ns;

end process;

end architecture RTL;

Veja que a dependência (HALF_ADD) é incluída no test bench, fazendo o mapeamento com o circuito que iremos estimular.

library lib_VHDL; use lib_VHDL.HALF_ADD;

Para compilar o test bench, abra um arquivo compil_BENCH e copie o seguinte Script:

vdel -lib ${PATH_WORK}/libs/lib_BENCH -all

vlib ${PATH_WORK}/libs/lib_BENCH

vmap lib_BENCH ${PATH_WORK}/libs/lib_BENCH

vcom -work lib_BENCH TB_HALF_ADD.vhd

Faça-o executável e execute-o:

chmod +x compil_BENCH ./compil_BENCH

OBS 1: Note que se você desejar testar somente o circuito PORTA_AND.vhd por exemplo, basta fazer um test bench para esse circuito, mapeá-lo de forma correta e ajustar compil_BENCH.

OBS 2: Se você estiver usando Verilog, o mapeamento é feito com:

`include "caminho/para/HALF_ADD.v"

5. ModelSim

Chegou a hora de visualizar os resultados. Lance o ModelSim:

vsim &

Veja as bibliotecas de trabalho criadas:

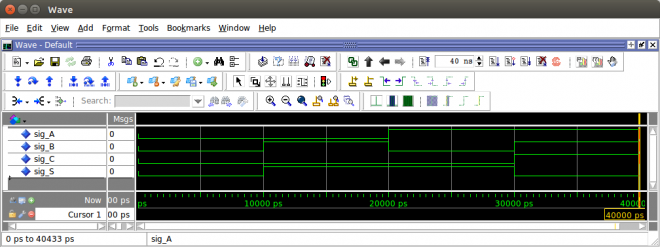

Dê dois cliques no tb_half_add.vhd (lib_BENCH), na próxima tela “jogue” os sinais para a janela Wave, configure o tempo de simulação (40 ns é suficiente) e execute!

Importante: Qualquer alteração nos códigos circuitos e/ou test bench, ao recompilar tudo no terminal não precisamos relançar o ModelSim, basta apertar o botão Restart (à esquerda da caixa de tempo) e tudo será atualizado.

Conclusão

Para projetos complexos que contêm uma grande quantidade de circuitos a serem implementados, essa prática organiza e facilita bastante o desenvolvimento do projeto. Para mais informações sobre os comandos disponibilizados pelo ModelSim, você pode fazer o download dos manuais nos seguintes links:

Espero que tenham gostado do artigo, fiquem à vontade para dar sugestões. Abraço a todos e muita paz!

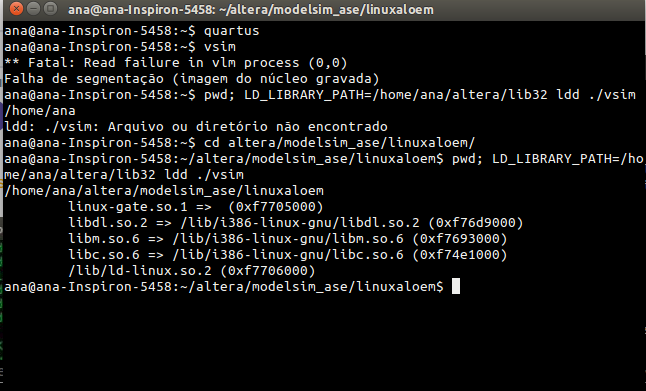

olá fui compilar o programa no terminal e deu erro de segmentação, joguei um comando na pasta linuxaloen e parece q ta puxando as lib erradas: alguma ideia de como arrumar?

olá, qnd eu rodo o modelSim da erro de segmentação no terminal, alguma ideia de como corrigir? Parece q ta puxando as lib erradas p compilar o programa

Esse erro acontece quando vou compilar. Alguma ideia do que seja?

Bruno,

Você configurou a variável PATH?

Você pode me mostrar o diretório que você instalou o modelsim?

Att,

Gabriel Villanova