Esse é o primeiro de uma série de artigos que visa trazer diversas informações de como desenvolver um bom código em Verilog.

Estados do Bit

Primeiramente vou apresentar todos os estados que os bits podem ter em um design com Verilog. Esse fato é muito importante pois impacta no desenvolvimento do projeto e sempre ter isso em mente ajuda a não cometermos gafes simples. Em HDL, todo bit pode ter os seguintes estados:

Operadores em Verilog

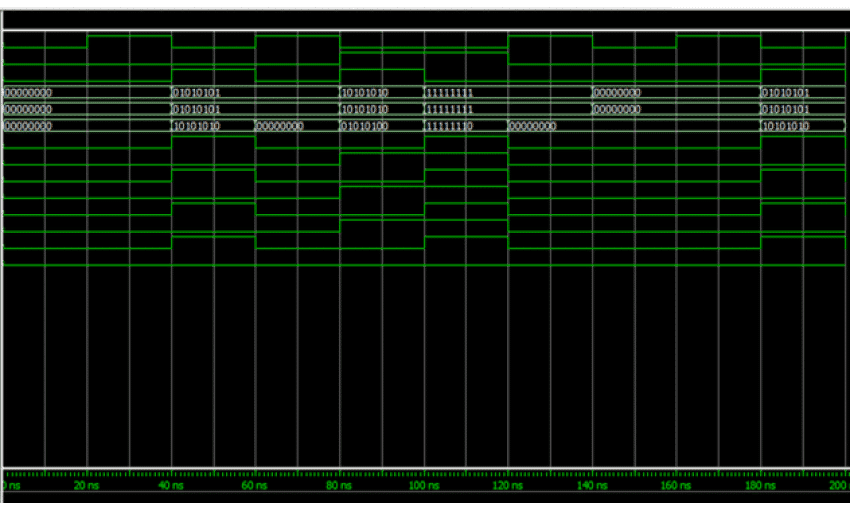

Vamos criar um módulo bem simples de hardware descrevendo seu comportamento em Verilog. Conforme foi discutido no post de Rodrigo Pereira sobre a implementação de um processador em Verilog, o modelo comportamental descreve exatamente como um circuito deve funcionar, utilizando uma linguagem HDL, e deixa a responsabilidade da criação da lógica e da simulação correta para as ferramentas de síntese.

Conforme André Prado cita em seu artigo sobre sistemas digitais, no nível comportamental o sistema é descrito em função do seu comportamento, é uma representação funcional do mesmo. Estamos, nesse caso, preocupados em descrever o que acontece na saída do sistema quando há uma alteração em uma entrada, é a relação direta de entrada/saída.

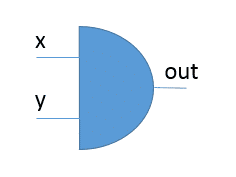

Uma porta AND, ilustrada na figura 1, pode ser reproduzida simplesmente como:

// Exemplo de Modelo Comportamental em Verilog de uma porta AND // Rodrigo Pereira - 16/03/2015 module EXEMPLO_AND ( x, y, out); // declaração do nome do módulo AND input wire x, y; // entrada de dados - um bit output wire out; // saída de dados - um bit assign out = x & y; // circuito AND utilizando a chamada assign em Verilog endmodule // final do módulo AND

Abaixo demonstro um código para um circuito com 3 portas lógicas descrito na figura 2.

// Exemplo de Modelo Comportamental em Verilog de um circuito com 3 portas logicas

// Thiago Lima - 16/04/2015

module EXAMPLE_2 (

a,

b,

c,

e,

f

);

input

a,b,c; // sinais de entrada um bit

output

e,f; // saidas um bit

wire

ab, d;

assign ab = a & b;

assign d = ~c;

assign e = ab | d;

assign f = a | b;

endmodule

Note algumas características interessantes do módulo escrito em Verilog:

- A palavra module inicia o módulo;

- Depois dos parenteses, há um ponto-e-virgula;

- Entradas são identificadas com a palavra input e as saídas com a palavra output;

- Os fios intermediários são identificados com a palavra wire;

- O modulo é finalizado por endmodule.

Todas as operações são realizadas em paralelo. Veja que para o circuito combinacional mostrado anteriormente, o caminho mais rápido é relativo a operação:

assign f = a | b;

Confira abaixo todos os operadores que podem ser utilizados com Verilog.

Operadores unitários

| + | a = b + c ; | // Soma , adição binaria |

| – | a = b – c ; | // Subtração, subtração binaria |

Operadores de todos os bits

| | | a = |b ; | // OR para todos os bits de b |

| & | a = &b ; | // AND para todos os bits de b |

| ^ | a = ^b ; | // XOR para todos os bits de b |

| ~| | a = ~|b ; | // NOR para todos os bits de b |

| ~& | a = ~&b ; | // NAND para todos os bits de b |

| ~^ | a = ~^b ; | // XNOR para todos os bits de b |

Operadores de bit-wise

| ~ | a = ~b; | // inverte b |

| | | a = b | c; | // OR bit a bit |

| & | a = b & c; | // AND bit a bit |

| ^ | a = b ^ c; | // XOR bit a bit |

| ~| | a = b ~| c; | // NOR bit a bit |

| ~& | a = b ~& c; | // NAND bit a bit |

| ~^ | a = b ~^ c; | // XNOR bit a bit |

Operadores de igualdade

| = | a = b | a recebe o valor de b |

| == | a == b | O valor de a é igual ao valor de b? |

| === | a === b | O valor de a é igual ao valor de b? Inclui os estados Z e X. |

| != | a != b | O valor de a nao é igual ao valor de b? |

| !== | a !== b | O valor de a nao é igual ao valor de b? Inclui os estados Z e X. |

Saiba mais sobre Verilog

PROCESSADORES PROGRAMÁVEIS – como projetar um processador em VERILOG – Arquitetura – parte 1

PROCESSADORES PROGRAMÁVEIS – como projetar um processador em VERILOG – Organização – parte 2

PROCESSADORES PROGRAMÁVEIS – como projetar um processador em VERILOG – Codificação – parte 3

Formas de representar um sistema digital

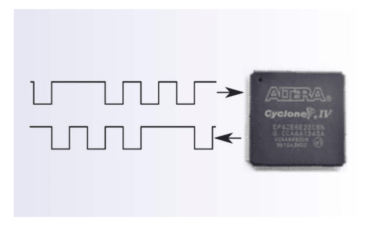

Tutorial de Modelsim: Verificando o VHDL antes de programar o FPGA

Tutorial de Verilog – Operadores Lógicos e Aritméticos Shift Right e Shift Left

No exemplo 1, nas linhas 4 e 5, qual a necessidade de definir o tipo como wire? Por padrão, entradas não são sempre wire? E saídas sem definir o tipo como reg também já não são wire por padrão?

Muito boa pergunta Fábio. Realmente não existe a necessidade da definição do tipo WIRE em entradas (na linha 4), eu costumo colocar por seguir a premissa de que devemos ter a consciência de tudo que estamos declarando, nesse sentido, todos os meus códigos sempre estarão com este padrão. Já a linha 5 se dá pela necessidade de ser uma saída de um bloco combinacional. Obrigado por questionar. Espero ter ajuda em algo.

Olá Rodrigo, obrigado pelo retorno.

Ainda em relação a linha 5, você também não tem necessidade de dizer que é um wire porque a saída também é do tipo wire por padrão, podendo assim ser usado no comando assign sem nenhum problema. Abraço.

Realmente, é força do hábito. Minha resposta está mal escrita, deixei a entender que era obrigatório, obrigado pela correção. Eu costumo definir sempre por conta de certificações de código, que em geral pedem que o tipo seja explicitamente declarado. Isso mostra como a linguagem é bem poderosa. Grato e sucesso.

Opa, tudo bem? Cara, to precisando fazer um filtro FIR com 8 Taps e 8 bits. Tem alguma referência bibliográfica pra me indicar? Preciso de uma luz. Obrigado.