Tanto o núcleo Cortex M0+ como o Cortex M0, implementam a arquitetura ARMv6-M e possuem arquitetura Von Neumann. São microcontroladores de 32 bits de baixo custo desenvolvidos pela ARM, que pretendem ocupar o lugar de micros bem simples, que realizam funções específicas ou que demandam baixo consumo de energia. Se comparado ao seu irmão Cortex M0, veja o que mudou no M0+:

Cortex M0+: Dois estágio de pipeline

Essa arquitetura apresenta uma novidade: opera com dois estágios de pipeline apenas. Essa característica permite que o processador acesse menos a memória flash, e, assim, permite menor consumo, se comparado com uma mesma atividade do núcleo Cortex M0, que tem três estágios de pipeline, tal como os núcleos Cortex M3 e o ARM7.

As sombras de branch também são reduzidas e isso propicia um tempo de chamada à função bem pequeno e interrupções com latência menor.

Cortex M0+: Acesso a IOs em um só ciclo

Essa característica interessante dos Cortex M0+ permite que os estados de cada pino sejam monitorados ou alterados em um só ciclo. Assim, CIs pequenos podem oferecer um controle do estado individual de seus pinos. É possivel mudar o estado de um pino na frequência igual à metade da frequência de operação do microcontrolador. Por exemplo, caso o microcontrolador esteja operando a 12 MHz, é possível que todos os pinos digitais do microcontrolador oscilem a 6 MHz.

Cortex M0+: MPU – Unidade protegida de memória

O Cortex M0+ suporta execução em nível previlegiado ou não previlegiado. Além disso, possui MPU – em oito regiões programáveis que podem ser utilizadas por um RTOS para criar regras de acessos e permissões para as diferentes tarefas rodando ao mesmo tempo. Ao fazer isso, são criados níveis de proteção no sistema, impedindo que uma aplicação em execução corrompa a memória de outras tarefas ou do próprio kernel do RTOS. Essa característica, no entanto, é opcional e só está presente nos Cortex M0+ da Freescale, família KM. Nenhum outro micro com núcleo Cortex M0+ possui MPU.

Cortex M0+: Realocação de tabela de vetores

O processor com arquitetura Cortex-M0+ suporta realocação de tabela de vetores. Isso permite realocação de vetores de exceção durante o tempo de execução.

Cortex M0+: Debug

O Cortex M0+ possui um solução de debug de baixo custo de trace baseado no uso de Micro Trace Buffer.

Uma pequena porção da SRAM pode ser alocada para isso pelo programador. O MTB armazena nessa área reservada todas as informações de trace relativas à essa instrução como se fosse um buffer circular. Quando o processador é parado, uma análise dessa região de SRAM pode ser realizada. Ele permite, assim, verificação do histórico de execução de instruções passadas.

Pode, além dessa forma, parar a execução quando o software passa por uma determinada instrução, para realizar seu trace.

A interface de debug é a SWD, 2 pinos ou JTAG.

MTB está presente nos microcontroladores Cortex M0+ da Freescale e da NXP. Não é encontrado, no entanto, nos micros da ATMEL. A memória utilizada para Trace é compartilhada com a memória SRAM nos microcontroladores da Freescale e NXP. Portanto, para realizar um trace, é interessante escolher um microcontrolador com um pouco mais de SRAM que a aplicação final demanda. Até 8 KB, para os micros da Freescale, podem ser utilizados para análise detalhada do que acontece durante a execução do código.

Cortex M0+: Fabricantes

Apenas quatro fabricantes possuem microcontroladores Cortex M0+. Veja a seguir:

Freescale

A Freescale possui diversos microcontroladores que já implementam a arquitetura Cortex M0+ e já os produz há mais tempo que seus concorrentes, hoje Atmel e NXP. Possui em todas as famílias suporte a debug utilizando a ferramenta livre OpenOCD. Detalho abaixo as famílias Freescale Cortex M0+:

- Freescale Kinetis E – feito para ser utilizado em equipamentos que trabalham em ambientes ruidosos e/ou hostis pois possuem alta imunidade a ruído. Podem operar com cristal interno, de 32 kHz e 20 MHz, e com cristal externo. Opera em 5V e suporta grandes variações de temperatura.

- Kinetis KE02 – primeira linha de microcontroladores dessa família – já é lançado com 10 microcontroladores de 3 opções diferentes de encapsulamento ( 32, 48 e 64 LQFP )

- Freescale Kinetis L, que são os microcontroladores de uso geral, e podem operar a até 48 MHz com cristal externo ou 4 MHz com oscilador interno. Apresentam um consumo bem baixo de corrente em seus modos especiais de economia de energia.

- Kinetis KL0x – Microcontroladores básicos e de menor preço e capacidade de memória e recursos

- Kinetis KL1x – De uso geral

- Kinetis KL2x – Micros com periférico USB OTG – Low Speed e Full Speed

- Kinetis KL3x – Microcontroladores com interface LCD

- Kinetis KL4x – Uma mistura do 2x e 3x – Microcontroladores com interface LCD e USB OTG Low e Full Speed

- Freescale Kinetis M é dedicado para dispositivos medidores de energia. Ele possui, como destaque, 2 a 4 canais de 24 bits ADC sigma-delta, ISO-7816 para leitura de smart cards, interface com display, um ou dois Amplificadores de ganho variável e características de segurança, como detector de tamper e gerador de números aleatórios. Três microcontroladores diferentes estarão disponíveis para venda, com encapsulamento MAPBGA 44, QFP 64 e QFP 100. É o M0+ mais veloz fabricado até hoje – opera até 50 MHz. São os únicos M0+ do mundo atualmente com MPU. Ainda não existe nenhum datasheet completo de componente no site da Freescale, tampouco User Manual dessa família de microcontroladores.

NXP

- NXP LPC800 – Essa família, lançada em 2012, conta já com 5 diferentes microcontroladores, cada um com um encapsulamento diferente. Os micros já lançados contam com até 20 pinos. A NXP deixa claro nessa linha que quer utilizar esse microcontrolador como dispositivo de entrada e vem pra ser um forte competidor dos microcontroladores de 8 e 16 bits. Pode operar até a 30 MHz com cristal externo, ou 12 MHz com oscilador interno, sem necessidade de cristal. O que chama atenção nesse microcontrolador é sua matriz de configuração, que permite que pinos digitais de diferentes funções sejam recolocados em diferentes posições, inclusive durante operação, e possui um micro de 8 pinos com encapsulamento DIP8. Do ponto de vista do desenvolvimento de software, possui ferramentas visuais que permitem configurar os pinos de maneira fácil. Além disso, a comunidade mbed possui suporte às duas placas de desenvolvimento com microcontroladores dessa família.

ATMEL

- ATMEL SAM D20 – Recém lançada, as novidades mais interessantes desse componente são o periférico específico para aplicações touch e uma inovadora forma dos periféricos se comunicarem sem passar por DMA ou sem que o core se preocupe com isso. Em outubro será comercializado o primeiro microcontrolador dessa família, o SAMD20J18, encapuslamento LQFP64, o mesmo que está no Evaluation KIt SAM D20 Xplained Pro. Opera até 48 MHz e possui oscilador interno de 8 MHz. Do ponto de vista de software, tem já suporte no ATMEL Studio, com diversos exemplos prontos pra usar.

Silicon Labs (antiga Energy Micro)

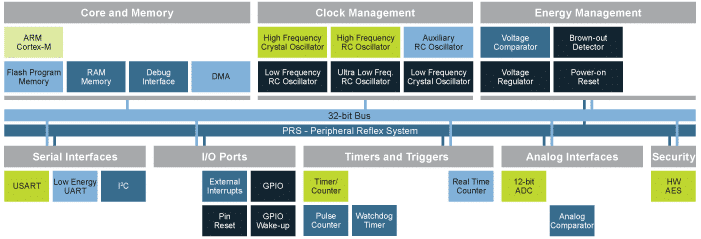

A linha de microcontroladores denominada ?EFM32ZG Zero Gecko, com 16 part numbers diferentes, tem até 32 KB de Flash e 4 KB de RAM, possuem capacidade de funcionar até 24 MHz com cristal externo. Como diferencial de mercado, possuem ADCs de 12-bits operando a até 1 Mbps. Alguns destes componentes também tem criptografia AES 128 em hardware. Essa linha era Cortex M0 e foi atualizada no fim de 2012 para Cortex M0+. Incorporou, assim, todas as características fundamentais para se atingir um consumo menor com relação ao núcleo anterior, M0.

Resumo

Referências

Canal ARMflix: Video Tutorial on ARM Cortex-M Series – Debug and Trace