O “Reduced Instruction Set Computer V”, RISC-V de forma abreviada, foi desenvolvido na Universidade da Califórnia em Berkeley por Krste Asanovic e David A. Patterson junto com parceiros industriais. O projeto surgiu de uma série de programas de pesquisa acadêmica sobre desenvolvimento paralelo de software e hardware.

A licença Berkeley Source Distribution (BSD) é uma chave que se difere de outras arquiteturas de conjunto de instruções (ISAs). Ela permite que os usuários projetem, fabriquem e vendam núcleos RISC-V sem royalties, enquanto as implementações patenteadas não precisam ser abertas a clientes ou concorrentes.

O RISC-V é permanente?

Um dos objetivos do RISC-V era uma pequena ISA aberto e otimizada para processadores rápidos, poderosos e com baixo consumo de energia. Ele pode ser facilmente implementado em FPGAs, ASICs e CPUs personalizadas e suporta todas as microarquiteturas, a maioria das linguagens de programação e pilhas de softwares. A ISA é corrigida para que o código escrito hoje continue a ser executado em futuros cores de processadores uma vez que eles usem a mesma ISA básica com extensões idênticas.

A RISC-V International, sucessora da Fundação RISC-V, supervisiona a tecnologia. Os autores e proprietários originais transferiram seus direitos para esta fundação.

O RISC-V fornece três ISAs de bases diferentes: RVI32I para hardware de 32 bits, RV64I para 64 bits e RV128I para 128 bits. Uma variante especial do RVI32I para sistemas embarcados é o RV32E com apenas 16 registradores.

Os comandos RV32I são baseados em seis formatos:

- Comando Tipo R: operações de registrador para registrador

- Comando Tipo I: operações imediatas curtas e operações de carregamento

- Comando Tipo S: salvando dados word (palavra)

- Comando Tipo B: ramificação condicional

- Comando Tipo U: imediatos superiores

- Comando Tipo J: instruções de salto

Esses formatos são a base para comandos inteiros, como: controlar, carregar/salvar, manipulação de registradores e depuração. No RV32I, todas essas instruções têm 32 bits de largura e usam apenas um ciclo de clock. Isso é muito diferente de outros ISAs, como ARM-32 ou x86-32, onde os comandos requerem vários ciclos.

Nos últimos anos, muitos fabricantes desenvolveram núcleos RISC-V, CPUs e MCUS, o que permitiu que a tecnologia amadurecesse e superasse os problemas iniciais.

Silício com uma ISA moderna

Uma das empresas pioneiras em núcleos RISC-V é a Andes Technology, membro do RISC-V International. Seu principal produto atual é o núcleo AX45MP de 64 bits.

Este IP de CPU multicore é um processador superescalar de 8 estágios baseado na arquitetura AndeStar V5. Ele suporta as extensões padrão RISC-V “G (IMAC-FD)”, os comandos de compressão de 16 bits “C”, a extensão DSP/SIMD “P” (rascunho), a extensão de interrupção de nível de usuário “N” e as extensões de desempenho/função da Andes para acesso mais rápido à memória e processamento de ramificação, bem como a extensão personalizada da Andes (ACE) para adicionar comandos personalizados. Ele apresenta um MMU para aplicativos baseados em Linux, uma previsão de ramificação para execução eficiente de ramificação, cachês de comando/dados de nível 1 e armazenamento local para acesso de baixa latência.

O multiprocessador simétrico AX45MP suporta até quatro cores e um controlador de cache de nível 2 com comando e pré-busca de dados. O Coherence Manager implementa o protocolo MESI para gerenciar a ligação do cache de nível 1, incluindo a adesão de E/S para mestres de barramento sem cache. Outros recursos do AX45MP incluem ECC para proteção contra erros leves no armazenamento de nível 1/2, controlador de interrupção em nível de plataforma (PLIC) com extensões para despacho vetorial e preempção baseada em prioridade, CoDense, StackSafe para melhorar a qualidade do software e QuickNap, PowerBrake, e WFI para gerenciamento de energia.

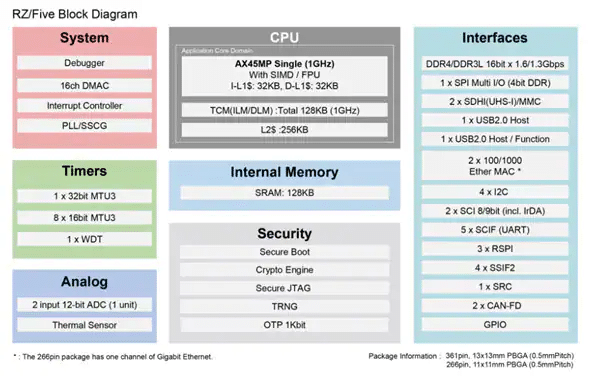

A Renesas Electronics implementou este núcleo no silício funcional. O microprocessador RZ/Five inclui um core de CPU RISC-V de 1,0 GHz (AX45MP Single) e uma interface DDR3L/DDR4 de 16 bits. Ele também possui várias interfaces, como Gbit Ethernet, CAN e USB 2.0, tornando-o adequado para aplicações como controle de gateway de infraestrutura social de nível básico e gateways industriais (Figura 1).

O RZ/Five (Figura 2) é oferecido em pacotes BGA-361 de 13 mm x 13 mm e BGA-266 de 11 mm x 11 mm. A variante BGA-361 contém uma interface Gigabit Ethernet de 2 canais. Já a variante BGA-266 oferece uma interface Gigabit Ethernet de 1 canal.

A placa de avaliação ajuda a determinar se o RZ/Five é adequado para resolver problemas de projeto. Ele fornece uma plataforma completa de demonstração e desenvolvimento para o microprocessador RZ/Five RISC-V. O RZ/Five MPU possui um core de CPU RISC-V de 1,0 GHz (AX45MP Single) e uma interface DDR3L/DDR4 de 16 bits. O dispositivo também possui uma variedade de interfaces, como Gbit Ethernet, CAN e USB 2.0, tornando-o ideal para controlar gateways de infraestrutura social e gateways industriais básicos.

O kit da placa de avaliação consiste em uma placa de módulo (SOM) (Figura 3) e uma placa de suporte. A placa base também pode ser usada com os módulos RZ/G2L, RZ/G2LC e RZ/V2L baseados no padrão SMARC v2.1. Esse design permite ao usuário uma avaliação contínua e flexível entre esses dispositivos.

O Futuro do RISC-V

A arquitetura aberta combinada com o moderno sistema de pipeline torna os cores RISC-V uma séria ameaça aos núcleos IP patenteados e fechados. A ausência de branches atrasados e códigos de status permite uma estrutura de CPU enxuta. À medida que mais empresas de design e fabricação de hardware implementam o RISC-V de silício, esse conjunto de instruções pode desempenhar um papel muito dominante no mercado de semicondutores.

Artigo escrito por Marcel Consée e publicado no blog da Mouser Electronics: RISC-V Is Slowly Establishing Itself

Traduzido pela Equipe Embarcados. Visite a página da Mouser Electronics no Embarcados

(*) este post foi patrocinado pela Mouser Electronics.

Bacana!

Quero ver um mundo open source.

Seria interessante convidar o Carlos de Paula ( https://www.linkedin.com/in/carlosedp/ ), que é o embaixador da RISC-V International para o Brasil, para uma entrevista.

Excelente artigo. Temos várias apresentações sobre RISC-V na Embarcados TV. A novidade aqui é a Renesas, uma das grandes empresas mundiais de microcontroladores, oferecendo core RISC-V. Até então havia apenas a Gigadevice. Portanto concordo que a adoção tem sido lenta. Mas em uma visão mais ampla do uso de CPU nas mais diversas aplicações , a adoção do RISC-V é um fenômeno !!!! Acho que vale a pena fazer uma apresentação atualizada do uso do RISC-V.