Este artigo é continuação da série Intel 8051 e tem como principal objetivo caracterizar o mapa de memória no Intel 8051. Todos os dispositivos da família 8051 têm o espaço de endereçamento distinto para o programa e para os dados. Essa divisão entre programa e dados foi apresentada no artigo de introdução como sendo característica da arquitetura de Harvard.

Memória de Programa

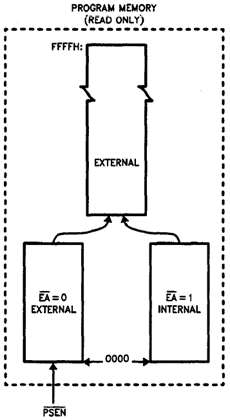

A memória de programa pode apenas ser lida. Internamente esses dispositivos possuem 4K bytes (padrão) de memória, contudo essa capacidade pode ser expandida para 64K bytes utilizando uma memória externa. Isso é ilustrado na Figura 1.

O pino EA determina se a memória de programa externa será utilizada. De modo geral:

- Quando EA é zero, todas as operações são realizadas na memória externa;

- Quando EA é um, os primeiros 4K de endereços são acessados internamente.

Além disso, para realizar o acesso à memória externa o sinal PSEN (Program Strobe Enable) é gerado pela CPU.

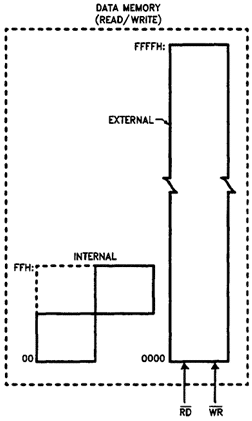

Memória de Dados

A memória de dados também pode ser expandida. Neste caso, os sinais RD e WR são gerados pela CPU conforme a operação executada. Para memória de dados, a instrução utilizada determinará se o acesso será interno ou externo.

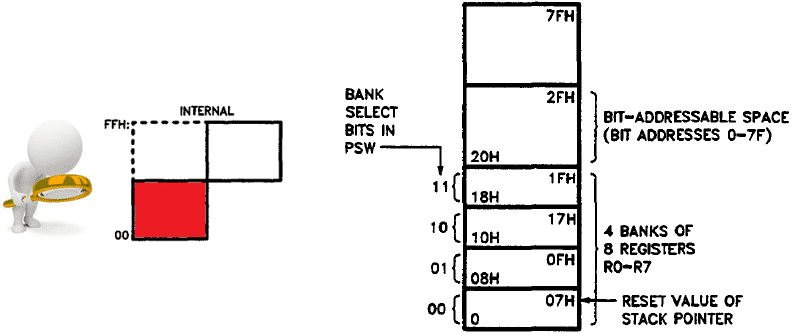

Conforme a Figura 2, internamente a memória de dados é dividida em regiões específicas e de propósito geral. Essas definições serão apresentadas na sequência.

Seções da Memória de Dados

A memória de dados é dividida em duas seções: Low-RAM e High-RAM.

A seção Low-RAM, ilustrada na Figura 3, corresponde ao espaço de endereçamento de 0x00 à 0x7F, isto é, os primeiros 128 bytes. Essa região é composta por quatro bancos de registradores, espaço de propósito geral e de bytes endereçáveis bit a bit.

Os bancos de registradores são nomeados como RB0, RB1, RB2 e RB3. Cada banco de registrador possui 8 registradores, portanto ocupam 32 bytes, e o espaço de endereçamento vai de 0 até 1FH (31). A região de bytes endereçáveis bit a bit, ilustrada na Figura 4, ocupa os endereços 20H à 2FH. Portanto, existem 16 bytes endereçáveis bit a bit, ou 128 bits endereçáveis.

O endereço dos bits é mostrado na Figura 5.

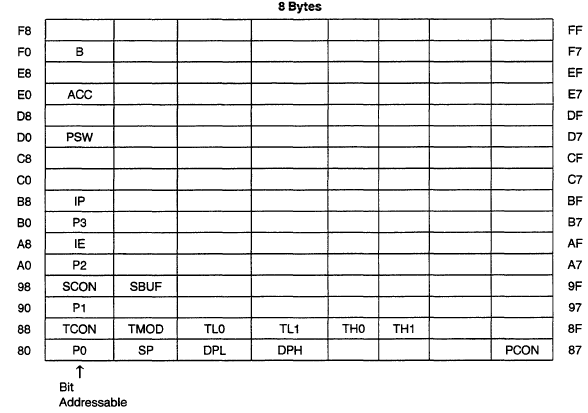

O Espaço de propósito geral corresponde ao espaço de endereçamento que vai de 0x30 a 0x7F. Os outros 128 bytes da memória de dados (High-RAM, ilustrado na Figura 6) são divididos em duas categorias. No entanto, isso não deve ser entendido como uma divisão do espaço de endereçamento, pois existem duas formas de acesso a essa região da memória. Quando o acesso realizado é direto (discutiremos isso em outro artigo) a região acessada será a de registradores de funções específicas. Já se o acesso é indireto, a região é considerada de propósito geral. Cabe ressaltar que essa região não está presente em alguns dispositivos.

- Propósito geral:

- Espaço de endereçamento: 0x80 a 0xFF;

- Não está presente em alguns microcontroladores;

- Modo de endereçamento: indireto.

- Registradores de funções especiais:

- Espaço de endereçamento: 0x80 a 0xFF;

- Modo de endereçamento: direto.

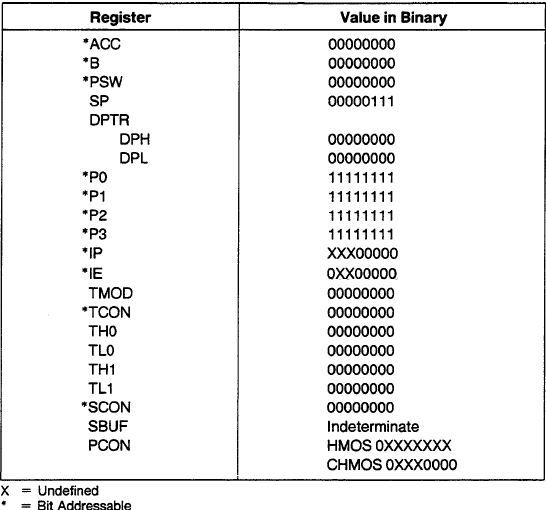

Os registradores de funções especiais são listados abaixo conforme os módulos correspondentes:

- Temporizadores/Contadores: TH1, TL1, TH0, TL1, TCON e TMOD;

- Portas I/O: P0, P1, P2 e P3;

- Stack Pointer: SP;

- Power Save: PCON;

- UART: SCON e SBUF;

- Interrupções: IE e IP;

- Uso geral: ACC e B;

- Ponteiro DPTR: DPH e DPL;

- Status: PSW.

De modo geral, os registradores especiais localizados nos endereços finalizados em 0H ou 8H são endereçáveis bit-a-bit (0x80 à 0xF7). O endereço dos registradores é mostrado na Figura 7.

Referências

- [1] MCS® 51 Microcontroller Family User’s Manual.

- Destaque para a Imagem Destacada.