Continuando a apresentação do TMS320F2812, neste artigo serão apontado alguns módulos e registradores relacionados com inicialização e configuração do modo de operação do DSP.

Reset e Clock

No artigo anterior foi mencionada a fonte de clock do DSP. Essas opções de clock são definidas no momento de reset do DSP, que pode ocorrer pelo pino XRS (RS, na Figura 1) ou pelo módulo watchdog timer. Isso é ilustrado na Figura 1.

De modo geral, o clock principal pode ser externo (diretamente de um cristal na entrada XCLKIN – limitado em 35MHz), ou interno, utilizando um circuito PLL com base na entrada XCLKIN. A utilização do PLL é definida pelo pino XPLLDIS. Quando ocorre o reset, o PLL é habilitado se o pino estiver em zero. O diagrama das fontes de clock é mostrado na Figura 2.

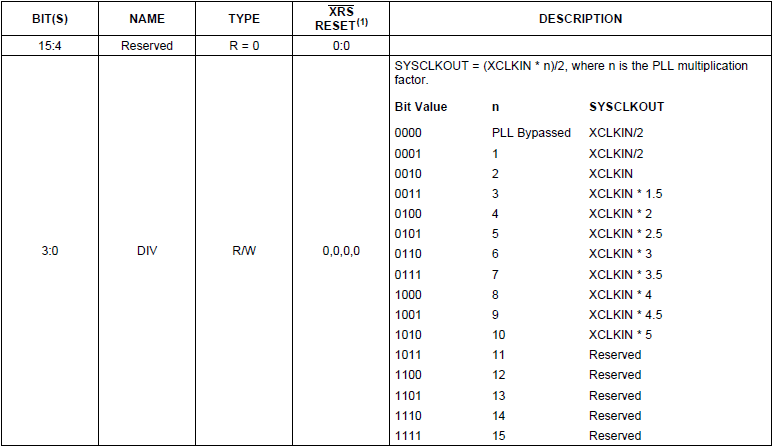

Quando o PLL é selecionado, sua frequência de operação é determinada pelo registrador PLLCR. A partir de 4 bits, a frequência de operação é definida da seguinte maneira: SYSCLKOUT = (XCLKIN * n) / 2, em que ‘n’ é fator de multiplicação selecionado. Esse registrador é mostrado na Figura 3.

Watchdog Timer

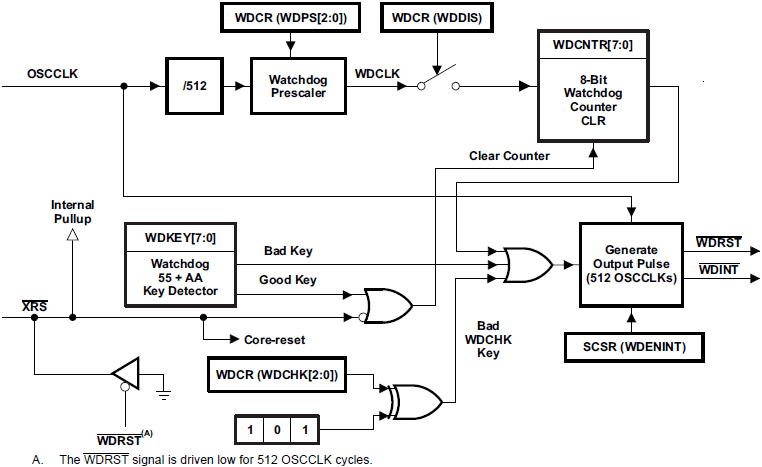

É importante destacar que o watchdog timer (Figura 4) é habilitado quando o dispositivo entra em operação, tendo como fonte de clock a entrada XCLKIN, denominado OSCCLK.

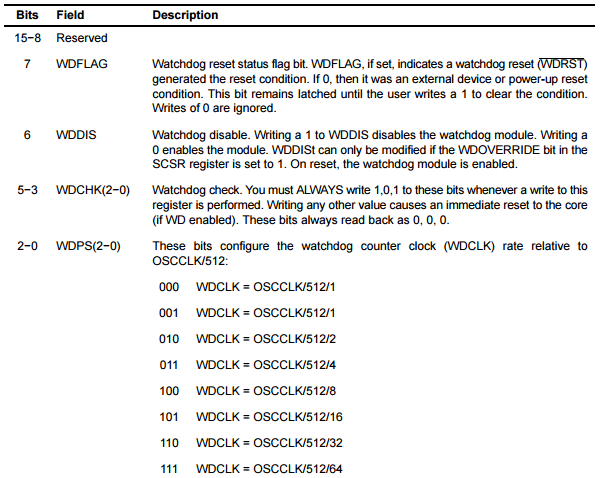

A configuração do watchdog timer é realizada pelo registrador WDCR, mostrado na Figura 5. Para manipular tal registrador é necessário alterar também os 3 bits WDCHK(5:3). Assim, em qualquer operação de escrita o valor 101 (5) deve ser armazenado nesse campo. Além de ser utilizado para verificar se a aplicação está fora do fluxo normal de operação, o watchdog pode ser utilizado para retornar dos modos de IDLE/STANDBY. Cabe ressaltar que em modo STANDBY somente o watchdog é mantido em operação (se habilitado).

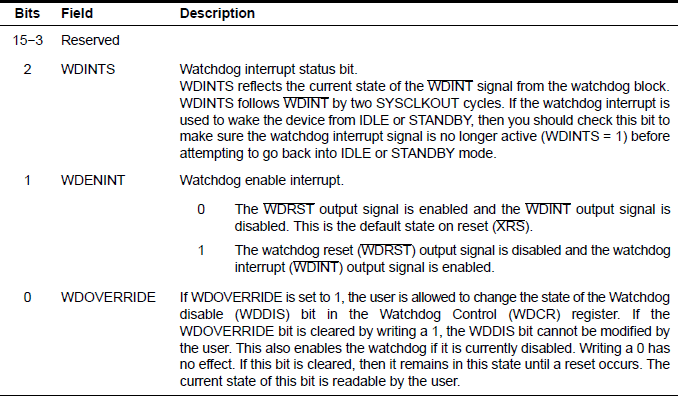

Quando o watchdog estoura, o DSP é mantido em reset durante 512 ciclos de clock (XCLKIN). Essa configuração pode ser alterada no registrador de controle e status (SCSR – Figura 6). O campo WDENINT determina se o watchdog gera um sinal de reset ou um sinal de interrupção.

Para reiniciar o contador do watchdog é necessário escrever a sequência de reinicialização do registrador WDKEY. A sequência de valores 0x55 e 0xAA reinicia o valor do contador, caso contrário o sinal de reset é gerado.

Sistema de Interrupção

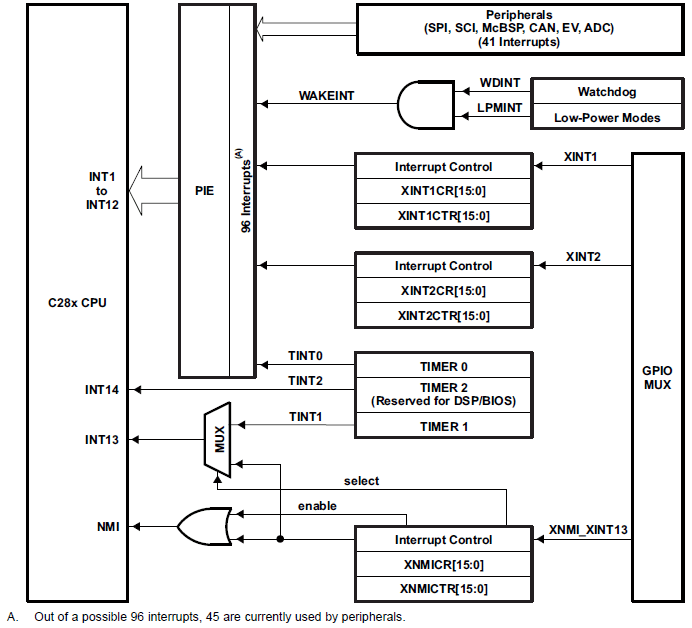

A CPU possui 12 blocos de interrupção que são controlados pelo PIE (interrupções geradas por periféricos), sendo que cada bloco possui 8 fontes de interrupção. Assim, 96 fontes de interrupção podem ser selecionadas. Dessas 96 fontes de interrupção, 45 são geradas por periférico enquanto o restante é reservado para futuras implementações. O sistema de interrupção é mostrado na Figura 7.

Quando uma interrupção ocorre, a instrução TRAP faz o desvio do programa para o endereço especificado no vetor de interrupção. O local dos vetores de interrupção são determinados por pinos e bits de controle. Para posiciona a tabela de interrupções no controlador PIE o pino VMAP deve estar 1 durante a operação de reset. Além disso, o bit PIEN do registrador PIE_CTRL deve ser ativado.

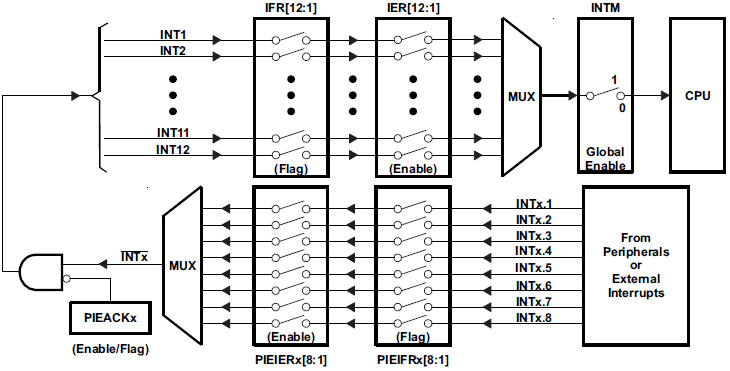

É importante destacar que o endereço 0 desse vetor de interrupção corresponde ao ponto de entrada do evento de Reset. No entanto, quando o PIE está habilitado esse endereço não é válido, pois não existe na tabela do PIE. O mecanismo de multiplexação das fontes de interrupção é mostrado na Figura 8.

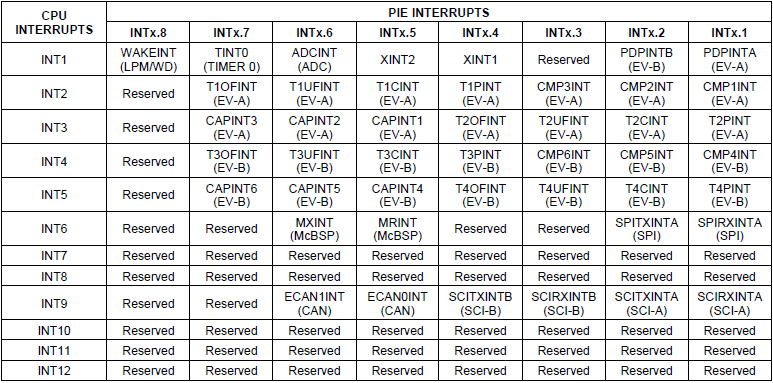

A tabela de interrupções é suas respectivas fontes e mostrada na Figura 9.

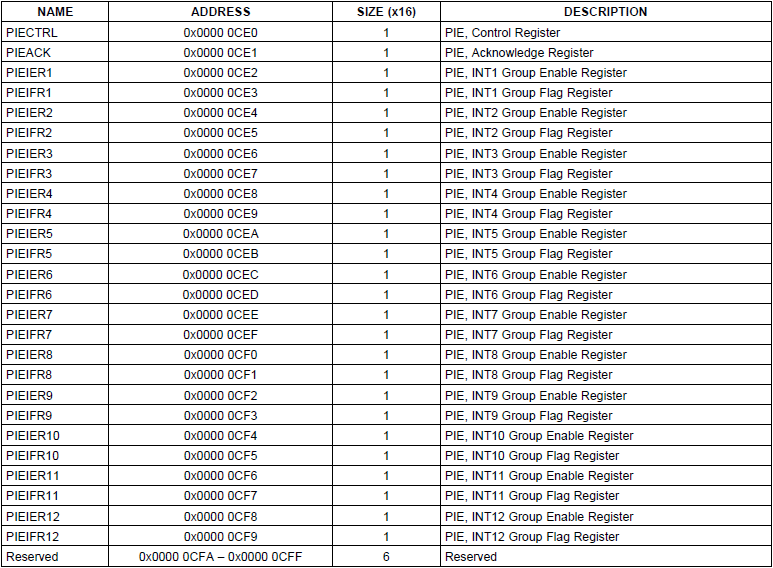

Além dessas fontes, outras duas podem ser geradas pelos timers ou externamente. As fontes INT1~INT14 são ditas mascaráveis, pois são controladas por registradores (PIEIER e PIEIEF). Já o sinal NMI causa uma interrupção direta na CPU, pois não pode ser controlada (ativada/desativada). Os registradores que controlam as interrupções internas são mostrados na Figura 10.

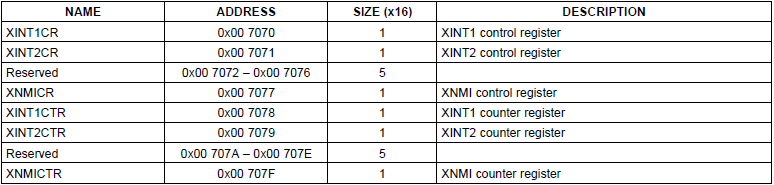

Já as interrupções externas são controladas pelos registradores mostrados na Figura 11.

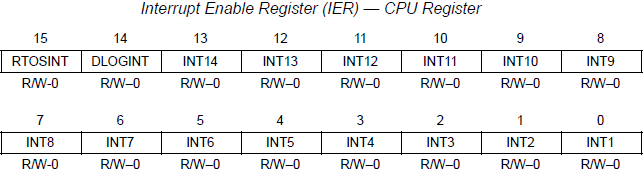

Além disso, as interrupções do DSP são controladas pelo registrador IE (Figura 12) e pelo bit global de interrupções.

/*Habilita interrupções globais*/

asm(" CLRC INTM");

Controle de Clock dos Periféricos

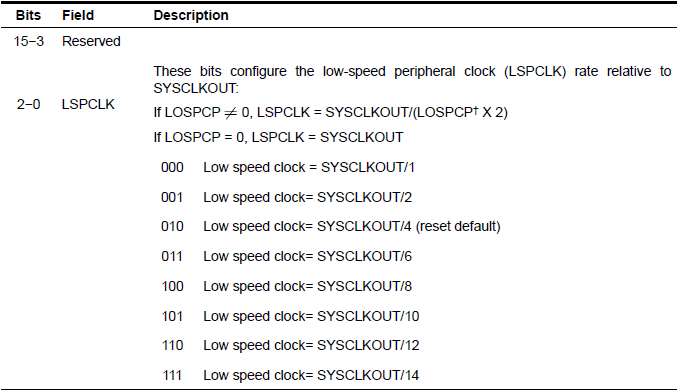

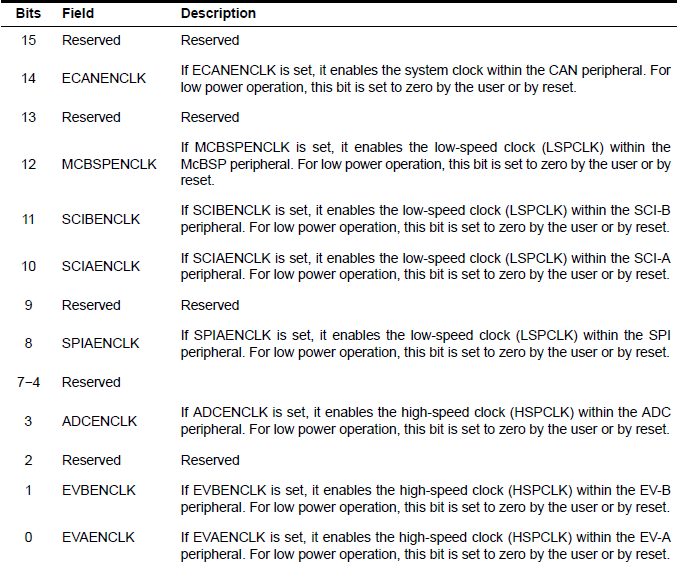

O clock do DSP é dividido em outros dois sinais: HSPCLK (High-Speed Peripheral Clock) e LSPCLK (Low-Speed Peripheral Clock). Tais sinais são utilizados como fonte de clock dos periféricos e podem ser configurados no registrador HISPCP e LOSPCP.

Além disso, cada periférico tem o clock habilitado no registrador PCLKCR (Figura 15). Essa característica possibilita reduzir o consumo do DSP, permanecendo habilitado somente o clock dos periféricos utilizados.

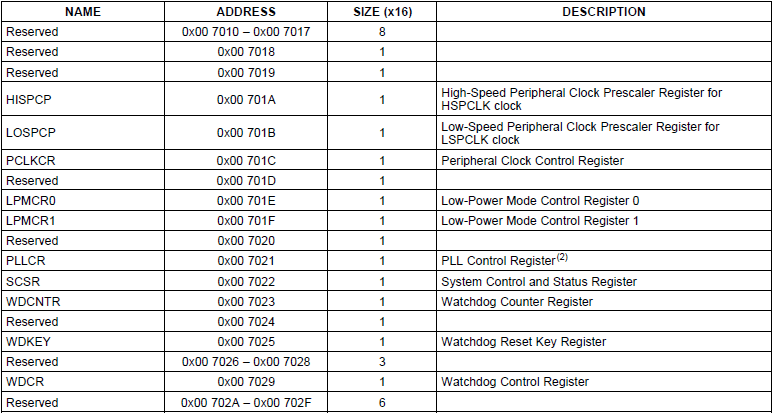

Os registradores descritos até o momento têm um mecanismo de proteção contra escrita que é manipulado a partir das instruções EALLOW e EDIS. Assim, é necessário desativar o mecanismo de proteção usando a instrução EALLOW, realizar a operação de escrita e, posteriormente, ativar a proteção novamente. Esse procedimento evita que os registradores sejam alterados por algum erro durante a execução do programa. Tais registradores são mostrados na Figura 16.

Referências