Olá, caro leitor! Este artigo tem o intuito de expor, de forma resumida, o conceito de co-simulação. Após conceituar o assunto, será demonstrado um projeto básico utilizando duas ferramentas bem conhecidas: Matlab/Simulink e ModelSim. O objetivo principal é demonstrar como simular sistemas compostos por elementos descritos em diferentes níveis de linguagem e abstração.

Design, Validação e Verificação

Durante o desenvolvimento de um sistema a utilização de técnicas de modelagem e simulação torna-se um fator significante. Nesse sentido, verificar e validar são práticas essenciais para garantir a qualidade do projeto, manter a conformidade com os padrões, atender aos requisitos, eliminar os erros de projeto e posteriormente maximizar o desempenho. Atualmente existem diversas ferramentas de software de apoio, permitindo que um projeto seja desenvolvido e simulado em partes individuais e depois integrados num sistema completo.

Testbench

Uma forma de analisar o comportamento de um sistema é a partir da utilização de testbenches. Um testbench utiliza diversos cenários de teste para estimular um sistema e obter uma resposta. Desse modo, um cenário define um conjunto de entradas de teste, já o sistema quando responde a estes estímulos gera uma resposta. Nesse contexto, um testbench pode ser considerado uma ferramenta para verificação e validação. Cabe ressaltar que nesse processo são utilizados softwares de simulação, que possuem seus prós e contras. Vale lembrar ainda que o sucesso da simulação não garante a funcionalidade do projeto, no mais, o aprofundamento dessas questões não estão no escopo do artigo.

Para exemplificar, considere o multiplexador descrito em verilog que foi apresentado no artigo do Thiago Lima.

// Embarcados - Use como quiser e de os créditos // Exemplo - Implementação de um multiplexador // Thiago Lima - 10/11/2015 module MUX6( A, B, S, X); input wire A, B; // As entradas sao A e B input wire S; // O sinal de selecao é S output wire X; // O sinal de saida é X wire S0_inv, a1, b1; not u1( S0_inv, S ); and u3( a1, S0_inv, A ); and u4( b1, S, B ); or u5( X, a1, b1 ); endmodule

O testbench para esse módulo é mostrado abaixo. Note que para cada conjunto de entrada A, B e S é possível avaliar o comportamento do multiplexador. Esse procedimento é realizado na simulação, sendo o ‘$display’ utilizado para exibir todos os sinais.

// Embarcados - Use como quiser e de os créditos

// Exemplo - Implementação de um testbench para o multiplexador

// Thiago Lima - 10/11/2015

module MUX6_TB;

reg A_tb, B_tb, S_tb;

wire X_tb;

integer i;

MUX6 dut( A_tb, B_tb, S_tb, X_tb);

initial

begin

A_tb = 1'b0; B_tb = 1'b0; S_tb = 1'b0; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b0; B_tb = 1'b1; S_tb = 1'b0; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b1; B_tb = 1'b0; S_tb = 1'b0; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b1; B_tb = 1'b1; S_tb = 1'b0; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b0; B_tb = 1'b0; S_tb = 1'b1; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b0; B_tb = 1'b1; S_tb = 1'b1; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b1; B_tb = 1'b0; S_tb = 1'b1; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

A_tb = 1'b1; B_tb = 1'b1; S_tb = 1'b1; #1

$display("A = %x, B = %x, S = %x, X = %x", A_tb, B_tb, S_tb, X_tb);

end

endmodule

Afinal, o que é Co-simulação?

O processo co-simulção é utilizado para validar um sistema que é composto por diferentes partes, por exemplo, hardware e software. Os modelos de co-simulação são categorizados como homogêneos ou heterogêneos.

- Num ambiente homogêneo todo o sistema é simulado utilizando a mesma ferramenta, isto determina que os modelos do sistema sejam especificados utilizando a mesma linguagem.

- No ambiente heterogêneo não é necessário que todas as entidades de um projeto sejam especificadas utilizando a mesma linguagem, ou ainda, a mesma tecnologia. Estes sistemas podem ser divididos em outras duas categorias: Backplane, que necessita de um ambiente para integrar os simuladores, ou Direct coupling, no qual os simuladores utilizam protocolos para trocar informação diretamente.

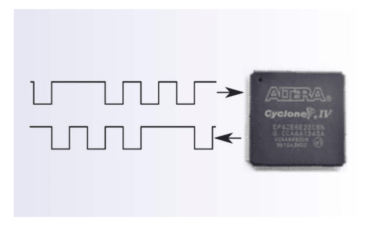

Neste artigo, será demonstrado a co-simulação heterogênea (vide Figura 1), um processo utilizado para validação de sistemas que é caracterizado por utilizar simuladores independentes que são executados paralelamente. O objetivo é fazer com que partes de um sistema sejam simulados utilizando ferramentas específicas.

Grosso modo, o processo de co-simulação tem como função realizar a comunicação entre os simuladores. Deste modo, um ambiente de co-simulação deve proporcionar um meio de comunicação entre os simuladores além de garantir a consistência na interação entre as partes.

Co-simulação HDL (HDL Cosimulation)

Como dito, o objetivo é demonstrar como simular sistemas compostos por elementos descritos em diferentes níveis de linguagem e abstração, neste caso será demonstrado a simulação de um módulo VHDL fazendo parte de um modelo do Simulink. Abaixo segue uma breve descrição sobre os dois softwares utilizados na co-simulação:

- Matlab/Simulink: Simulink® é um ambiente de diagramação gráfica por blocos utilizado para modelagem de sistemas. Tem suporte para simulação, geração automática de código, teste contínuo e verificação de sistemas embarcados. O toolbox que possui o componente de co-simulação HDL é chamado HDL Verifier;

-

ModelSim (PE 10.4a): ModelSim® é um ambiente de simulação de linguagens de descrição de hardware (HDL – Hardware Description Language) desenvolvido pela Mentor Graphics.

Utilizando a co-simulação de módulos HDL é possível verificar o comportamento de um sistema como um todo. Desse modo, a ferramenta de simulação HDL possibilita analisar o código HDL a nível RTL ou Gate Level. Por outro lado, o simulador de modelos permite analisar no nível de sistema o comportamento de vários elementos e, principalmente, a interação entre eles. Além disso, é possível verificar como as diferenças entre os resultados esperados e os resultados da simulação afetam o sistema, tornando-se uma ferramenta importante para validação.

Para mais informações sobre o ModelSim, consulte o artigo do Andre Prado.

Co-simulação na prática

Antes de iniciar a construção do sistema, é necessário estabelecer o canal de comunicação entre os simuladores. Sem entrar em muitos detalhes, a comunicação entre os simuladores pode ser estabelecida de diversas formas, por exemplo, via sockets ou memória compartilhada. Neste exemplo, a conexão será estabelecida utilizando um socket. Para isso, o comando mostrado abaixo deve ser executado na linha de comando do Matlab.

vsim('socketsimulink', 4449)

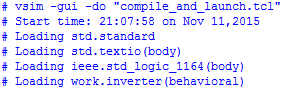

Algumas mensagens podem aparecer após a execução do comando, conforme a Figura 2. Neste exemplo, a versão do ModelSim utilizada não é padrão do toolbox instalado (HDL Verifier), contudo a interação entre os simuladores foi bem sucedida.

Após a execução do comando, o ModelSim será iniciado. Neste ponto, um projeto será criado para incluir um módulo VHDL. O código mostrado abaixo é um exemplo de tutorial do Matlab, sua função é inverter o valor da entrada e atribuir este valor na saída em cada evento de clock.

--------------------------------------------------------------------------------

-- EMBARCADOS (embarcados.com.br)

-- Artigo: Co-simulação HDL

-- Autor: Fernando Deluno Garcia

--------------------------------------------------------------------------------

-- Arquivo: inverter.vhd

-- Autor : MathWorks

-- Tutorial: https://www.mathworks.com/help/hdlverifier/ug/simulation-timescales.html?searchHighlight=inverter%20vhdl#bt9u4xl-80

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY inverter IS PORT (

inport : IN std_logic_vector := "11111111";

outport: OUT std_logic_vector := "00000000";

clk:IN std_logic

);

END inverter;

ARCHITECTURE behavioral OF inverter IS

BEGIN

PROCESS(clk)

BEGIN

IF (clk'EVENT AND clk = '1') THEN

outport <= NOT inport;

END IF;

END PROCESS;

END behavioral;

No ModelSim, acesse o menu File -> New -> Project e crie um projeto. Esse processo é mostrado na Figura 3.

Após criar o projeto, acesse o item Add Existing File e adicione o módulo VHDL mostrado acima, conforme a Figura 4.

Com o arquivo adicionado ao projeto, o próximo passo é compila-lo. Para isso, selecione o arquivo na aba Project e execute a operação de compilação como mostra a Figura 5.

Após a operação, analise o console Transcript para verificar se o processo de compilação ocorreu corretamente. Na Figura 6 é mostrado o resultado da compilação do módulo VHDL.

Finalizado o processo, o próximo passo é indicar para o simulink o arquivo que será simulado. No ModelSim, é necessário executar a operação mostrada abaixo.

vsimulink work.inverter

Após a execução do comando algumas mensagens serão exibidas, conforme a Figura 7.

Na tela de simulação, selecione os sinais que serão exibidos na linha do tempo, conforme a Figura 8.

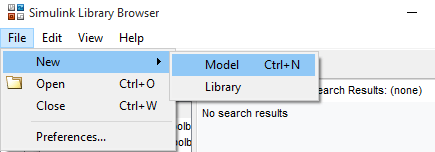

O próximo passo é criar um sistema no simulink. Para cria-lo acesse o menu Simulink Library no Matlab, em seguida crie um modelo para simulação. Esse processo é mostrado na Figura 9.

No Simulink Browser Library acesse o item ‘for “Use with Mentor Graphics ModelSim” presente no pacote “HDL Verifier”, conforme a Figura 10.

Selecione o item HDL Cosimulation para inserir no modelo, conforme a Figura 11.

A primeira configuração que deve ser realizada é a da conexão com o simulador HDL. Acessando as propriedades de conexão do bloco HDL Cosimulation, especifique o tipo de conexão socket e a porta 4449, conforme a Figura 12.

Ainda nas configurações, acesse a aba Ports e utilize a operação Auto Fill para exportar os sinais definidos na entidade do módulo VHDL. Esse processo é mostrado na Figura 13.

Em seguida remova os sinais previamente definidos no bloco. Apenas os sinais definidos no módulo VHDL devem estar presentes, conforme a Figura 14.

A Figura 15 mostra o bloco HDL Cosimulation configurado conforme o arquivo VHDL.

A Figura 16 mostra o cenário de simulação que será utilizado, cabe ressaltar que os tipos de dados utilizados nos componentes devem ser equivalentes. Os componentes utilizados são listados abaixo:

- Entrada clk: Para a entrada de clock foi utilizado o gerador de clock (Clock) configurado com frequência de 1000 Hz. A saída deste componente varia de 0 para 1 e de 1 para 0. Na sequência esses valores são convertidos (Data type conversion, Simulink) para booleano;

- Entrada inport: Para esta entrada foi utilizado um contador de 8 bits (Counter Free-Runing) com sample time de 5 milissegundos;

- Saída outport: A saída do módulo foi conectada ao componente scope.

Antes de iniciar a simulação é necessário realizar uma configuração fundamental, a relação do tempo de simulação entre os simuladores utilizados! Neste exemplo será utilizada a seguinte relação: 1 segundo no Simulink corresponde a 1 segundo no ModelSim. Conforme a Figura 17, esta opção é realizada na aba Timescales.

Feito isso, é necessário determinar o tempo no qual os sinais do bloco HDL são avaliados. As entradas utilizam o sample time do Simulink, já na saída foi definido um sample time de 1 milissegundo (1e-3), isto é, durante a simulação a saída outport será amostrada a cada 1 milissegundos. A Figura 18 mostra a configuração dos sinais de entrada e saída.

Para iniciar a simulação, basta definir o tempo total e executar a operação Run no meu do Simulink, conforme a Figura 19. No exemplo foi utilizado tempo total de 5 segundos.

A Figura 20 mostra a saída do sistema capturada pelo componente Scope após a finalização da simulação.

Como a simulação HDL é realizada no ModelSim os sinais também podem ser verificados no painel Wave, conforme a Figura 21. Cabe ressaltar que para realizar uma nova simulação é necessário reiniciar a simulação no ModelSim.

Conclusão

Nesse artigo, objetivou-se demonstrar que projetos de sistemas podem ser simulados utilizando diversos ambientes, isto é, que diferentes partes podem ser simuladas individualmente e depois integradas num processo chamado de co-simulação. Utilizando esta técnica um módulo descrito em VHDL foi simulado utilizando o software ModelSim, no entanto este módulo fazia correspondência a um sistema modelado utilizando o software Matlab/Simulink. Assim, foi possível determinar as entradas em um simulador e analisar o comportamento de um módulo simulado por outra ferramenta. Cabe ressaltar que os cenários de teste podem ser bem mais elaborados do que o demonstrado neste artigo, por exemplo, gerar casos de teste utilizando scripts do Matlab ou ainda adicionando mecanismos de validação entrada/resposta.

Para saber mais

- A versão trial do pacote HDL Verifier pode ser obtida neste link;

- A configuração de Sample Time e Timescales entre os simuladores é apresentada de forma detalhada nos tutoriais listados abaixo:

Referências

HDL Verifier: HDL Cosimulation

HDL Verifier: Cosimulation and FPGA-in-the-Loop in MATLAB-to-HDL Workflow

Crédito para a imagem destacada: https://pixabay.com/pt/espiral-escada-etapas-escadas-926736/

Muito legal esse tipo de integração com o Simulink, ví bastante gente fazendo de forma manual e independente no Matlab/Modelsim , mas dessa forma que você apresentou é bem interessante.

Olá, Caio.

Obrigado pelo retorno!

É bem interessante pelo fato de automatizar esse processo de integração entre as entradas/saídas dos modelos simulados. Realizar essa integração manualmente pode ser bem difícil para um sistema complexo.

Meu simulador não está lendo a derivada do erro de um sistema de nível T__T se eu colocar derivada discreta, será que dá certo?

Você adicionou o bloco de conversão de dados? É necessário adequar as entradas para o bloco do Modelsim.

sim,coloquei as entradas como “integer” e usei o datatype conversion.Mas a entrada da derivada do erro eu tenho dúvida: no erro, eu só discretizei (coloquei um z-¹(delay). na derivada do erro, na frente do bloco (du/dt) eu só discretizo, ou tenho que trocar esta derivada, para a derivada discreta?

usei o mesmo software do modelsim e ele não consegue carregar o arquivo .vhd pelo fato desta versão não conter o pacote “std” alguém pode me ajudar?