Olá, caro leitor! Este artigo é continuação da série Intel 8051 e tem como principal objetivo descrever o ciclo de execução de instruções.

O ciclo de Execução

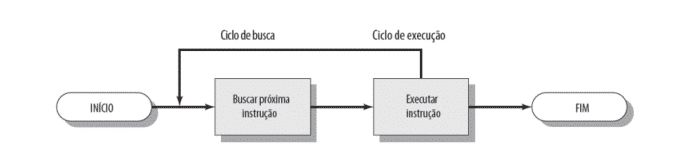

O ciclo de execução, ilustrado na Figura 1, corresponde às etapas realizadas pela CPU para que uma instrução seja buscada na memória, decodificada e executada.

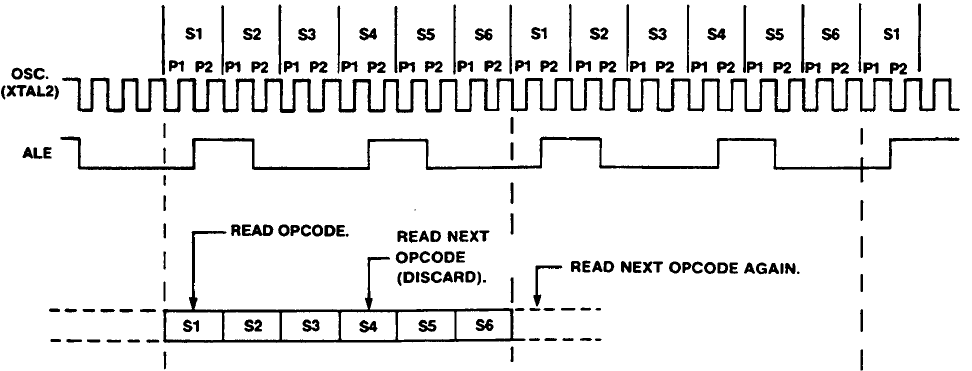

De modo geral, esse ciclo de execução é dividido em ciclos de máquina, sendo que cada ciclo de máquina é executado em 12 ciclos de clock. Além disso, cada ciclo de máquina é representado por um conjunto de estados nomeados de S1 à S6. Isso é mostrado na Figura 2, para o caso de uma instrução de 1 byte executada em 1 ciclo de máquina.

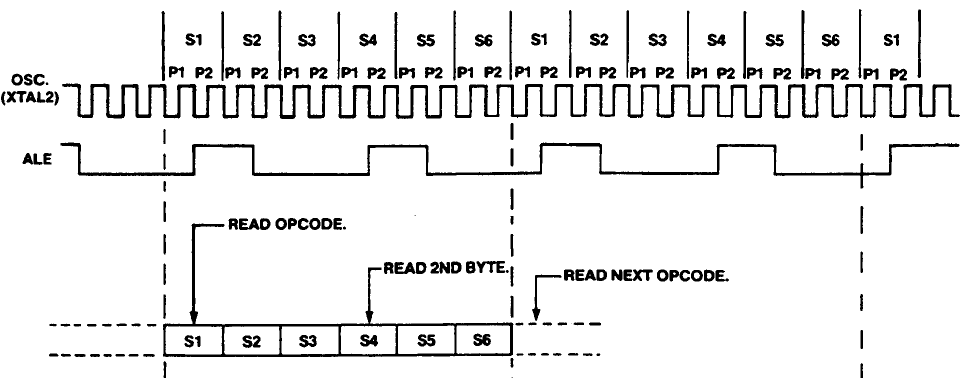

Conforme a Figura 3, existem ainda instruções de bytes que são executadas em 1 ciclo de máquina.

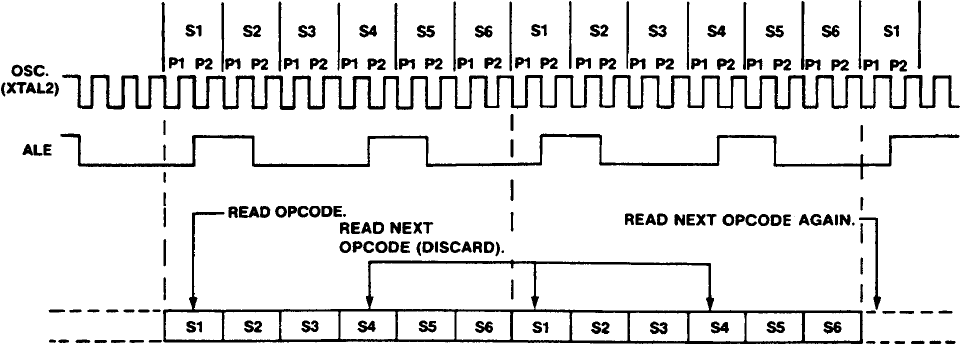

Portanto, com clock de 12 MHz a CPU pode alcançar 1 MIPS (para instruções de 1 ciclo), isto é, um milhão de instruções por segundo. Outras instruções, como indicado na Figura 4, necessitam de dois ciclos de máquina para serem executadas.

Interface com Memória Externa

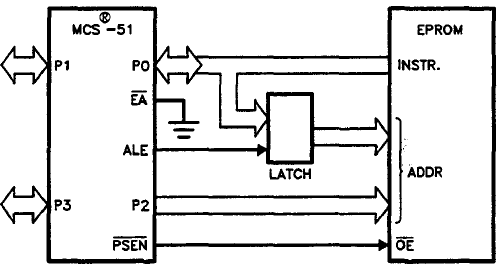

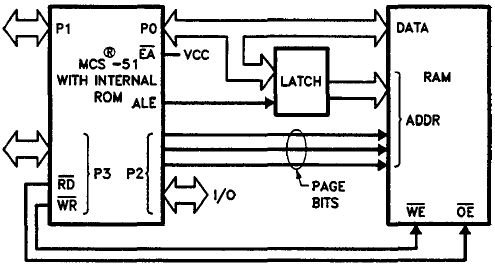

Durante o processo de execução, a CPU emite sinais para realizar as operações de leitura e escrita das memórias. Quando a memória externa (RAM e/ou ROM) é utilizada, um circuito latch deve ser adicionado para compartilhar o PORT 0 do microcontrolador. Isso se faz necessário pois a mesma porta que é utilizada para determinar o endereço acessado também serve para as operações do barramento de dados. Além disso, o pino EA é utilizado para indicar se a memória de programa será interna ou externa. Já os sinais PSEN, RD e WR são utilizados para as operações nas memórias externas e, nos dois casos, o sinal ALE (Address Latch Enable) é utilizado para habilitar o latch.

- Conexões da memória de programa externa.

- Conexões da memória de dados externa.

Os diagramas ilustrados nas figuras 7, 8 e 9 exibem o estado dos sinais de controle para os casos onde a memória externa é utilizada. Considerando a memória de programa externa, a CPU determina o endereço de 16 bits que será acessado. Esse endereço tem seu byte menos significativo colocado no PORT 0, e o mais significativo no PORT 2. Nesse momento a CPU ativa o sinal ALE, fazendo com que o circuito latch armazene esses 8 bits. Assim, a CPU desativa o ALE e memória continuará com o endereço selecionado. Por fim, o sinal PSEN é habilitado e, nesse momento, o conteúdo (instrução) do endereço selecionado é colocado no barramento de dados, isto é, no mesmo PORT 0.

O mesmo vale para memória de dados. A única diferença é que no processo de leitura o conteúdo do barramento de dados não é uma instrução. Cabe ressaltar que para a memória de dados o sinal RD especifica a operação de leitura.

Na operação de escrita, após a especificação do endereço a CPU determina o dado que será gravado na memória. Essa operação é realizada quando o sinal WR é ativado.

Características Gerais de Operação

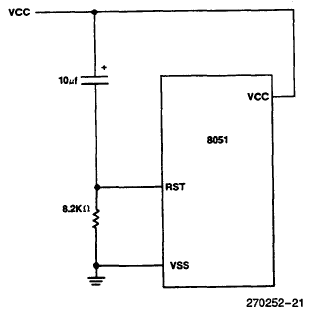

Para o sistema ser inicializado corretamente o pino de reset (RST) deve ser mantido em nível lógico 1 por pelo menos 2 ciclos de máquina (24 ciclos de clock). Na Figura 10 é mostrado um circuito comumente utilizado para reiniciar o microcontrolador no momento em que a alimentação é dada. Por um instante de tempo (circuito RC) o reset é mantido em 1 até que o capacitor fique carregado.

Após o reset, a CPU inicia sua execução a partir do endereço 0000H. Além disso, o sistema é configurado da seguinte maneira:

- O banco de registrador 0 é selecionado;

- O Stack Pointer é inicializado na posição 07H;

- Os ports são inicializados com todos os bits em 1;

- O conteúdo da memória RAM não é alterado.

Referências

- [1] MCS® 51 Microcontroller Family User’s Manual.

- [2] STALLINGS, W. Arquitetura e organização de computadores. Pearson Prentice-Hall, 8ª ed, São Paulo. 2010.

- Crédito da Imagem Destacada.

Acompanhando já cedo.

Vamos em frente.