No artigo anterior, falei sobre a importância do tamanho dos capacitores de desacoplamento, mas isto é somente a metade da história neste tema, já que igual ou mais importante que o tamanho, é um bom roteamento do capacitor.

Relembrando: o tamanho do capacitor de desacoplamento é importante, porque um tamanho maior implica um maior loop na corrente, o que leva uma maior indutância, a qual leva a uma maior impedância em alta frequência. O objetivo dos capacitores de desacoplamento é prover uma trilha de baixa impedância, assim, a posição do capacitor e o roteamento deste também possuem um papel fundamental.

Prioridade nos capacitores

O ideal é posicionar os capacitores o mais perto possível do pino do CI para, assim, não contribuir com a indutância da trilha e, ainda, deixar o mínimo da trilha suscetível a ruídos.

No artigo anterior, falei sobre misturar capacitores de diferentes capacitâncias e tamanhos, mas… qual seria o critério para decidir qual tem que ficar mais perto?

Quanto menor o capacitor (tamanho e capacitância), menor impedância para uma maior frequência e o ruído mais crítico para os CIs é o ruído de alta frequência. Além disso, se a capacitância é pequena, um pequeno aumento na indutância, dado pela distância da trilha do pino até o capacitor, pode igualar a parte capacitiva do capacitor para certas frequências. Assim, sempre os capacitores menores são os que tem a prioridade, e precisam estar o mais perto possível do CI.

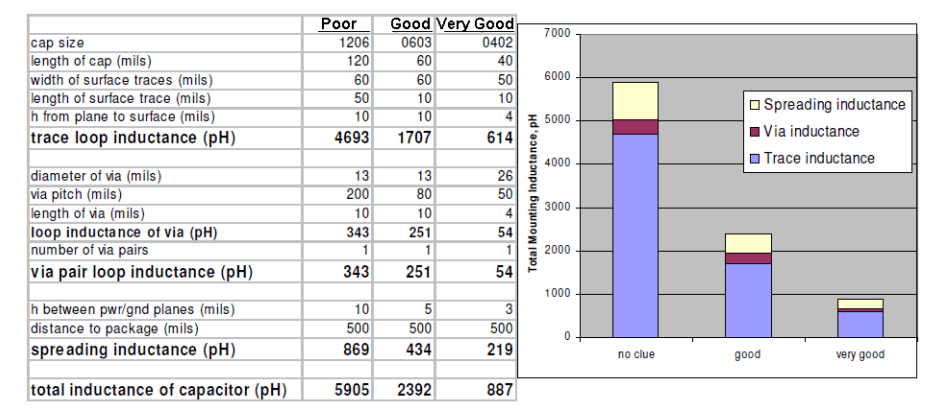

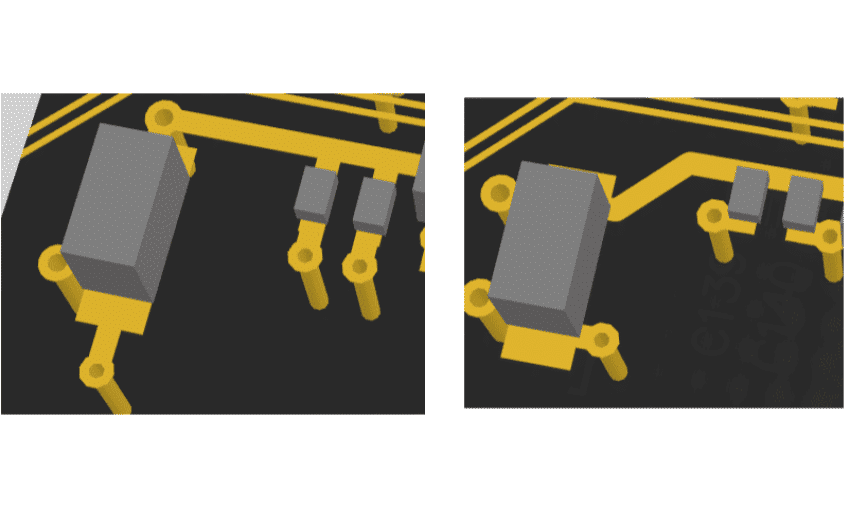

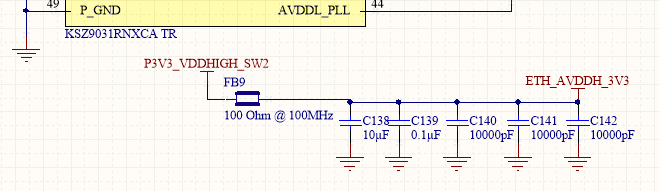

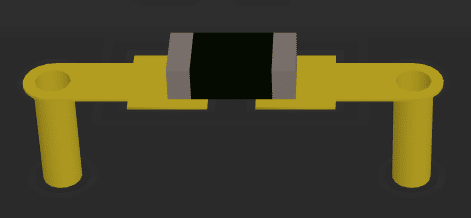

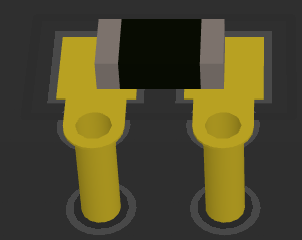

Na figura 1 e 2 pode-se olhar o posicionamento dos capacitores C140, C139 e C138 (10.000pF, 0.1uF e 10uF respectivamente), de uma linha de alimentação de um transdutor de ethernet que se utilize em um projeto, e pode-se olhar a ordem: quanto menor o capacitor, mais perto do pino de alimentação do CI ele precisa ficar.

Roteamento das trilhas do capacitor

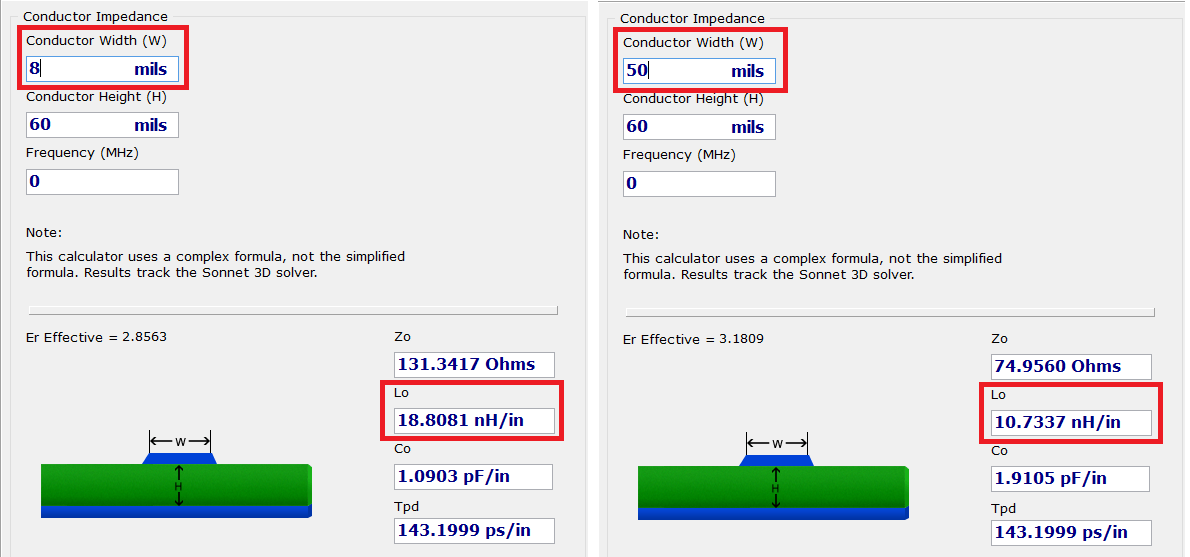

Um outro ponto importante é a geometria das trilhas, sendo que, idealmente, temos que fazer as trilhas com uma largura maior possível, já que, quanto mais estreita é uma trilha, maior indutância e, quanto maior a indutância, o efeito de desacoplamento do capacitor é menor.

Na figura 3, pode-se ver um print do software Saturn PCB (software gratuito e muito recomendado para o desenho de PCB), onde se vê a diferença produzida na indutância de uma trilha quando se utiliza uma trilha de largura 8 mils (esquerda) – o que é tamanho tipico para trilhas de sinais – e uma trilha de 50 mils (direita) – onde a indutância diminui quase pela metade.

Posição das Vias

A posição das vias no capacitor de desacoplamento pode afetar bastante a indutância do capacitor, já que elas têm direta influência no loop que faz a corrente. Na figura 4, pode-se ver o loop que a corrente faz quando há um mal posicionamento das vias para um capacitor. Por outro lado, na figura 5, pode-se ver o que acontece com esse mesmo loop com um correto posicionamento das Vias.

Agora, voltando ao exemplo dos capacitores de desacoplamento do transdutor de ethernet da figura 2, na figura 6 se apresenta, na esquerda, a forma desaconselhada de posicionar as vias e fazer o roteamento e, na direita, a forma correta, que foi a utilizada neste projeto.

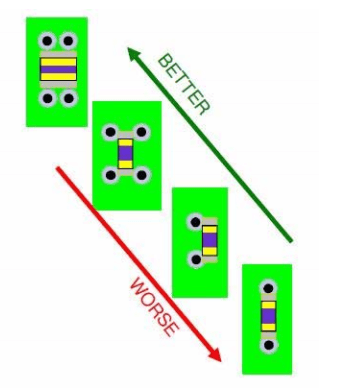

Na figura 7, pode-se ver uma imagem do application note AN 574 da ALTERA, onde se mostra a diferença entre um ótimo posicionamento das vias e um mal posicionamento delas. Nele se pode ver, além do que já foi explicado, que o ideal é utilizar mais de uma via para cada pino do capacitor.

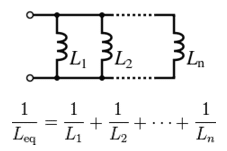

Isto, diferente do que muita gente pensa, generalmente NÃO é pela condutividade das vias. Na figura 8 se mostra, por médio dá Saturn PCB, as propriedades de uma via tipica 10/18. Ela conduz 2 Ampere, o que é mais do que a maioria dos CI digitais utilizam. Mas se destaca também, em vermelho, uma indutância muito alta na via; portanto, para efeitos práticos, em alta frequência, as vias modelam-se como indutores. E relembrando a teórica básica das redes elétricas… o que acontece com os indutores em paralelo? Sua indutância baixa!

É por isso que, quando olhamos as placas feitas pelos profissionais (placas gráficas, notebooks, celular, etc ), como selecionado em verde na figura 10, tem muitas vias para uma trilha/plano. Isto é para diminuir o efeito da indutância das vias!

Na figura 10 ainda se destacam três pontos já comentados neste artigo:

- A posição correta das vias nos capacitores (do lado de cada pino do capacitor);

- Prioridade nos capacitores: o capacitor menor o mais perto possível do pino (conector finger neste caso);

- A utilização de capacitores de diferentes tamanhos físicos.

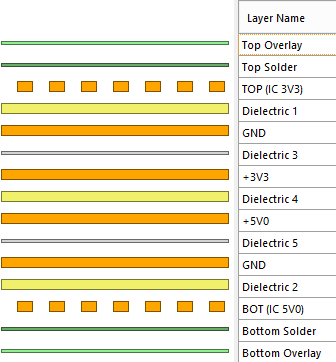

Posicionamento dos componentes e os planos de alimentação no stackup

Por último, você tem o loop que faz a corrente na altura do PCB. Assim, você, idealmente, tem que ter um planejamento de onde vai posicionar os componentes, na camada TOP ou BOTTOM e, também, de onde ficarão seus planos de alimentação, para assim diminuir, ao máximo, o loop da corrente.

Portanto, se temos, por exemplo, um PCB de 6 camadas, onde a camada 1 é TOP e a 6 é BOTTOM, e todos seus CIs são de tensão de 3V3 e 5V, você tem que idealmente por todos os CIs com uma alimentação de 3V3 na camada TOP e as camadas de alimentação destes CIs (+3V3 e GND) o mais perto possível da camada TOP (ou da camada BOTTOM) para, assim, ter o menor loop possível nestes CIs. E o mesmo vale para os CIs de alimentação de +5V. (O desenho do stackup é muito mais complexo. Este é um mero exemplo para esclarecer o assunto).

Este ponto, na prática, é muito difícil de cumprir, já que hoje se tem muitas linhas de alimentação para os diferentes CIs. Mas ainda sim, a recomendação é ter isto em conta e fazer o melhor possível.

Resumo

Para resumir um pouco, temos que cumprir certos pontos importantes para realizar um correto desacoplamento dos CIs de alta frequência:

- Seleção de capacitores: Quanto menor é a capacitância, menor tem que ser o tamanho capacitor para que este cumpra o efeito desejado;

- Prioridade no posicionamento: Idealmente todos os capacitores têm que ficar o mais perto possível do pino do CI, mas os de capacitância menor têm a prioridade;

- Vias dos capacitores: Busca-se uma indutância a mais baixa possível, assim as vias têm que ser posicionadas de uma forma que contribua com isto e, idealmente, se possível, por mais de uma via para, assim, diminuir a indutância das vias;

- Planejar o posicionamento dos CIs e os planos de alimentação: Idealmente para diminuir o loop que a corrente faz, temos que deixar os CIs de certa tensão o mais perto possível no stackup dos planos dessa mesma tensão. (o que é difícil de cumprir).

Você nem sempre vai poder cumprir todos estes pontos, mas o importante é ter em mente o efeito de cada um. Assim, seja por razões de orçamento ou por problemas no roteamento, saber que ponto você pode dar menor atenção e o que fazer para poder diminuir um pouco o efeito disto.

Por último, na figura 13, pode-se ver o resultado empírico na indutância quando aplicado o que foi dito neste artigo ou, em comparação, um roteamento amador.

Obs: Ao ler este artigo, você pode estar se perguntando se isto é um nível distante de seus atuais projetos, já que você não está desenhando placas gráficas, tablets, ou projetos com processadores, etc. Mas você pode ver que muitas destas recomendações (e as que eu darei nos próximos artigos sobre desenhos complexos em alta frequência e multicamadas) você também pode cumprir com facilidade e sem nenhum custo extra em desenhos mais simples. Assim, minha recomendação (que eu sigo de profissionais experts na área e com muitos anos de experiência na indústria) é que é melhor sempre seguir as boas práticas de desenho para todos seus projetos.

Além disto, de acordo com o que fala Eric Bogatin (um dos maiores especialistas nesta área) em seu livro “Signal and Power Integrity” as companhias de produção de CI estão mudando suas linhas de produção e, não faz sentido existirem diferentes linhas de produção para uns CIs de frequência X e outras linhas de produção para os CIs de frequência Y. Portanto, todos os CIs estão começando a sair para o mercado com a mesma tecnologia. A frequência de um microcontrolador X é muito baixa, mas ele foi feito em uma linha de produção onde produzem processadores Y. A frequência do microcontrolador X vai ser baixa, mas seu rise time (o qual é o verdadeiro problema da alta frequência) vai ser alto, o mesmo rise time do processador Y. Então, se o fabricante não faz algo para controlar o rise time (o que implica investir mais dinheiro), não estranhe se você comece a ter problemas associados à alta frequência em seu projeto com componentes de baixa frequência.

Se você tiver sugestões e críticas, por favor, faça-as que serão muito bem vindas.

Já pensou em escrever um livro sobre o assunto de melhores praticas de confecção de PCB?

Olá Boa tarde!! Uma dúvida que sempre tenho no desenvolvimento de PCbs é quanto ao plano de terra. Leio em artigos que é sempre bom ter um bom plano utilizando o maior tamanho posível , minimizando a indutância e também sobre técnicas de união de terras. Mas, uma coisa que vejo em algumas placas e quero saber qual é o correto é sobre como conectar os capacitores de desacoplamento para Ci’s, ou seja, no meu entender os mesmos não devem tocar ou estar ligados diretamente no plano. Porque desta forma a função de filtro e desacoplamento não é respeitada. Então,… Leia mais »

Opa!

Uma coisa que está implícito na figura 7 mas não foi explicitamente explorado é o uso de capacitores de geometria reversa, como os 0204 ou 0306. Esses capacitores possuem uma indutância muito menor do que os tradicionais.

Muito bom o artigo Javier! Por mais que o artigo seja para projetos mais complexos, como você ressaltou no final, tem muita PCB com capacitor de 10pF e PTH nos cristais da vida!

Javier, muito bom o Artigo. Você ministra treinamentos na área de projetos de PCB? Ou possui algum livro que aborde esse tema? Abraços!

Igo, perdão!, não tinha visto o post. Lamentavelmente não, gostaria no futuro poder fazer. Entretanto, nesta serie de artigos intentarei dar pequenas introduções para os temas de PCB. Obrigado pelo feedback!, abs Javier

Ótimo artigo! A área de PCB é uma das que menos recebe atenção. Encontramos muita coisa na internet falando de PCB mas geralmente de forma amadora. Quando se deseja saber algo mais profissional temos que recorrer a sites ou livros estrangeiros. Muito bom saber que começam a tratar o assunto de forma profissional aqui no Brasil.

Excelente artigo!

Obrigado Alexandre!, que bom que você achou util.