Os microcontroladores Arm® multicore representam um avanço significativo na tecnologia de sistemas embarcados, oferecendo a capacidade de realizar tarefas mais complexas, melhorar o desempenho das aplicações e reduzir o consumo de energia. Neste texto, exploraremos as diferentes configurações de microcontroladores Arm multicore e estratégias de otimização para maximizar as capacidades dos MCUs Arm multicore em sistemas embarcados.

Perfis de Arquitetura Arm Cortex

A arquitetura Arm, conhecida por sua eficiência e desempenho, é amplamente utilizada em aplicações que vão desde smartphones até sistemas de controle industrial. Os núcleos Arm vêm em diversas configurações de arquitetura, incluindo as séries Cortex-A, Cortex-R e Cortex-M, cada uma projetada para diferentes aplicações:

- Cortex-A (processadores de aplicação): Os processadores Cortex-A são projetados para alto desempenho e sistemas operacionais robustos como Android ou Linux. Aplicações típicas incluem smartphones, tablets, equipamentos de rede e sistemas industriais de alto nível.

- Cortex-R (processadores em tempo real): Os processadores Cortex-R priorizam tempos de resposta determinísticos e previsibilidade para aplicações em tempo real. São frequentemente usados em automação industrial, controle de motores, robótica e sistemas críticos de segurança, como os automotivos e de aviação.

- Cortex-M (microcontroladores): Os processadores Cortex-M enfatizam baixo consumo de energia, eficiência de custo e flexibilidade, tornando-os adequados para uma ampla gama de aplicações embarcadas. Exemplos incluem dispositivos vestíveis, sensores, dispositivos para casas inteligentes e aplicações de Internet das Coisas (IoT).

As configurações multicore podem melhorar o desempenho ao permitir processamento paralelo e manipulação eficiente de dados. Um processador multicore pode ser visualizado externamente de duas maneiras: como uma unidade única ou cluster — seja pelo projetista do sistema ou pelo sistema operacional — que pode abstrair os recursos subjacentes da camada de aplicação, ou como múltiplos clusters, em que cada cluster contém múltiplos núcleos.

A série Cortex-A de alto desempenho pode usar clusters para melhorar o desempenho e a eficiência energética. Por exemplo, alguns sistemas em chip (SoCs) baseados em núcleos Cortex-A podem agrupar vários núcleos com caches compartilhados e controladores de memória. As séries Cortex-R e Cortex-M focam principalmente no desempenho em tempo real e no baixo consumo de energia, respectivamente, e geralmente não implementam clusters no sentido tradicional. Elas podem ter configurações multicore, mas esses núcleos operam de forma independente, sem os recursos compartilhados associados às arquiteturas em cluster.

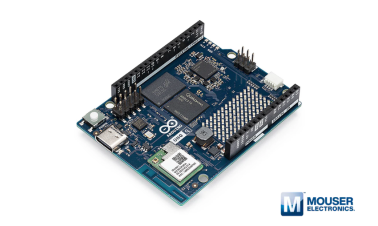

Hoje, até mesmo plataformas de microcontroladores de baixo custo, como o Raspberry Pi RP2040, possuem dois núcleos M0+. Isso significa que o hardware multicore está cada vez mais presente e não está restrito a produtos mais caros. No entanto, o hardware multicore não está isento de desafios. Independentemente de quão bem projetado seja o hardware, um código mal escrito ainda pode impactar negativamente o sistema durante as operações.

Estratégias de Programação

As seções a seguir oferecem dicas para programar software eficiente em microcontroladores Arm multicore.

Identifique o Paralelismo de Tarefas

O fundamento de uma programação multicore bem-sucedida é identificar oportunidades para execução paralela dentro de sua aplicação. Procure tarefas independentes que possam ser executadas simultaneamente, sem dependências de dados. Exemplos incluem:

- Processamento de dados de sensores: Vários núcleos podem lidar simultaneamente com dados de diferentes sensores.

- Processamento de sinais: Algoritmos como filtragem ou transformada rápida de Fourier (FFT) podem ser divididos entre múltiplos núcleos, distribuindo os cálculos intensivos em hardware.

- Tarefas de interface do usuário: Um núcleo pode gerenciar interações com o usuário enquanto outro realiza o processamento em segundo plano.

Escolha um Modelo de Programação Paralela

Depois de identificar o paralelismo, selecione um modelo de programação adequado para coordenar tarefas entre núcleos. Modelos comuns incluem:

- Primário/subordinado: Um núcleo principal distribui tarefas para outros núcleos subordinados e gerencia a comunicação. Simples, mas pode causar gargalos no núcleo principal.

- Multithreading: Cada núcleo executa sua própria thread, permitindo paralelismo mais detalhado. Exige sincronização cuidadosa para evitar condições de concorrência.

- Passagem de mensagens: Os núcleos se comunicam enviando mensagens, permitindo distribuição flexível de tarefas e balanceamento dinâmico de carga.

Pratique Codificação Eficiente

Algumas operações de software dependem de qual núcleo está executando o código. Por exemplo, a inicialização global geralmente é realizada por um único núcleo, seguida de inicialização local em todos os núcleos. Existem dois locais possíveis para identificar qual núcleo está executando o código:

- Multi-Processor Affinity Register (MPIDR_EL1): Este registrador mostra qual núcleo está executando o código, tanto dentro de um cluster quanto em um sistema multi-cluster.

- U-bit: Algumas configurações do processador indicam se é um cluster de núcleo único ou multicore.

Outros elementos de design para otimizar o software incluem:

- Modularidade do código: Código modular melhora a legibilidade, facilita a manutenção e simplifica a depuração.

- Gerenciamento de memória: O uso eficiente de memória é essencial. Desenvolvedores devem gerenciar pilha e heap com cuidado, evitar vazamentos de memória e usar acesso direto à memória (DMA) para operações intensivas.

- Eficiência energética: Otimizar o código para eficiência energética é crucial em dispositivos alimentados por bateria. Técnicas incluem modos de suspensão, redução de velocidades de clock e otimização do tratamento de interrupções.

Aproveite a Concorrência

A concorrência de tarefas é fundamental para microcontroladores multicore, pois permite o uso eficiente de vários núcleos, viabilizando a execução paralela de tarefas e melhorando o desempenho geral do sistema. Executar tarefas simultaneamente reduz a latência e aumenta a capacidade de resposta em aplicações sensíveis ao tempo. Além disso, a concorrência melhora o gerenciamento de recursos, distribuindo a carga de trabalho de maneira uniforme para evitar gargalos e maximizar a eficiência.

Métodos para aproveitar a concorrência incluem:

- Paralelismo de tarefas: Divida a aplicação em tarefas independentes que possam ser executadas simultaneamente. Prático para aplicações que podem ser fragmentadas em tarefas distintas.

- Paralelismo de dados: Realize a mesma operação em vários elementos de dados em paralelo. Beneficia tarefas como processamento de sinais e imagens.

- Sincronização: Sincronização adequada evita condições de concorrência e corrupção de dados. Microcontroladores Arm oferecem mecanismos como semáforos, mutexes e barreiras.

- Comunicação entre processadores (IPC): Mecanismos eficientes de IPC são vitais para sistemas multicore. Técnicas incluem memória compartilhada, passagem de mensagens e sinais de interrupção. A execução concorrente exige mecanismos para garantir consistência de dados e evitar condições de concorrência:

- Semáforos: Controlam o acesso a recursos compartilhados, como blocos de memória, evitando modificações simultâneas por múltiplos núcleos.

- Mutexes: Garantem acesso exclusivo a uma seção crítica do código, permitindo que apenas um núcleo execute por vez.

- Filas de mensagens: Núcleos trocam dados enviando e recebendo mensagens, facilitando a comunicação assíncrona.

Estratégias de Otimização

A otimização de software é essencial para microcontroladores multicore, pois afeta diretamente o desempenho e a eficiência. Um código bem otimizado minimiza instruções desnecessárias e utiliza eficientemente os recursos de hardware, como memória, permitindo melhor execução paralela entre núcleos. Isso pode gerar benefícios significativos no desempenho dos sistemas multicore enquanto reduz o consumo de energia.

Otimização de Software

As estratégias de otimização de software para microcontroladores multicore incluem:

- Otimizações do compilador: Utilize flags de otimização do compilador para melhorar o desempenho e reduzir o tamanho do código. Compreender os trade-offs entre diferentes níveis de otimização é crucial.

- Perfilagem e benchmarking: Perfis regulares da aplicação ajudam a identificar gargalos. Ferramentas como o Streamline Performance Analyzer da Arm fornecem insights valiosos.

- Otimização de cache: O uso eficiente de cache pode impactar significativamente o desempenho. Técnicas incluem bloquear o cache para seções críticas e otimizar estruturas de dados para eficiência de cache.

Otimização para Cache e Memória

Os processadores multicore frequentemente possuem hierarquias de cache complexas, e o uso eficaz desses caches é crucial para o desempenho.

- Localidade de dados: Coloque dados frequentemente acessados próximos na memória para melhorar a taxa de acertos no cache.

- Alinhamento de linha de cache: Garanta que as estruturas de dados estejam alinhadas com os limites de linha de cache para acesso eficiente.

- Minimizar compartilhamento falso: Evite colocar dados não relacionados na mesma linha de cache para prevenir invalidações desnecessárias.

- Otimização em Assembly: Para seções críticas do código, considere usar linguagem assembly para obter controle completo sobre o hardware e maximizar o desempenho.

Aproveitando Recursos de Hardware

Os microcontroladores Arm multicore modernos frequentemente fornecem mecanismos assistidos por hardware, como:

- Periféricos IPC: Canais de hardware dedicados para troca rápida de dados entre núcleos.

- Unidades de gerenciamento de memória (MMUs): Hardware que permite proteção e isolamento de memória entre núcleos, melhorando a segurança e a confiabilidade.

- Protocolos de coerência de cache: Mecanismos gerenciados por hardware para garantir consistência de dados entre caches de diferentes núcleos.

Depuração, Profiling e Testes

Ao implementar os métodos mencionados para otimizar software em microcontroladores multicore, espera-se alcançar aumentos significativos de desempenho e eficiência energética. No entanto, a codificação para sistemas multicore pode gerar consequências não intencionais. Por isso, o código deve ser testado e medido para garantir que está sendo executado de maneira eficiente em vários núcleos.

- Depuradores multicore-aware: Inspecione os estados individuais dos núcleos, canais de comunicação e primitivas de sincronização usando ferramentas de depuração como JTAG, SWD e recursos de depuração embarcados adequados aos microcontroladores Arm.

- Ferramentas de profiling: Identifique gargalos de desempenho e avalie a utilização dos núcleos para otimizar a distribuição de tarefas.

- Testes unitários: Implemente testes unitários para componentes individuais, garantindo confiabilidade antes de integrá-los ao sistema maior.

- Testes de integração: Teste a interação entre diferentes componentes do sistema, especialmente importante em ambientes multicore, onde as interações entre tarefas podem ser complexas.

Conclusão

Programar microcontroladores Arm multicore apresenta desafios únicos, mas também oferece o potencial de melhorias significativas de desempenho. Ao entender a arquitetura Arm, identificar e planejar cuidadosamente tarefas paralelas, adotar práticas de codificação eficientes, aproveitar a concorrência e aplicar estratégias de otimização, os desenvolvedores podem maximizar as capacidades desses dispositivos poderosos. Essa visão geral fornece uma base, mas dominar a programação de microcontroladores Arm multicore exige estudo aprofundado, experiência prática e engajamento contínuo com as mais recentes tecnologias e metodologias. A Arm oferece um guia introdutório para programadores, bem como treinamentos mais avançados para ajudar engenheiros a otimizar sua programação.

Artigo publicado por Mouser Electronics no blog da Mouser Electronics: Optimizing Software for Multicore Arm Microcontrollers

Traduzido pela Equipe Embarcados. Visite a página da Mouser Electronics no Embarcados

Excelente artigo. Sugiro, apenas, alterar a tradução do termo “race conditions” de “condições de corrida” para “condições de concorrência“.